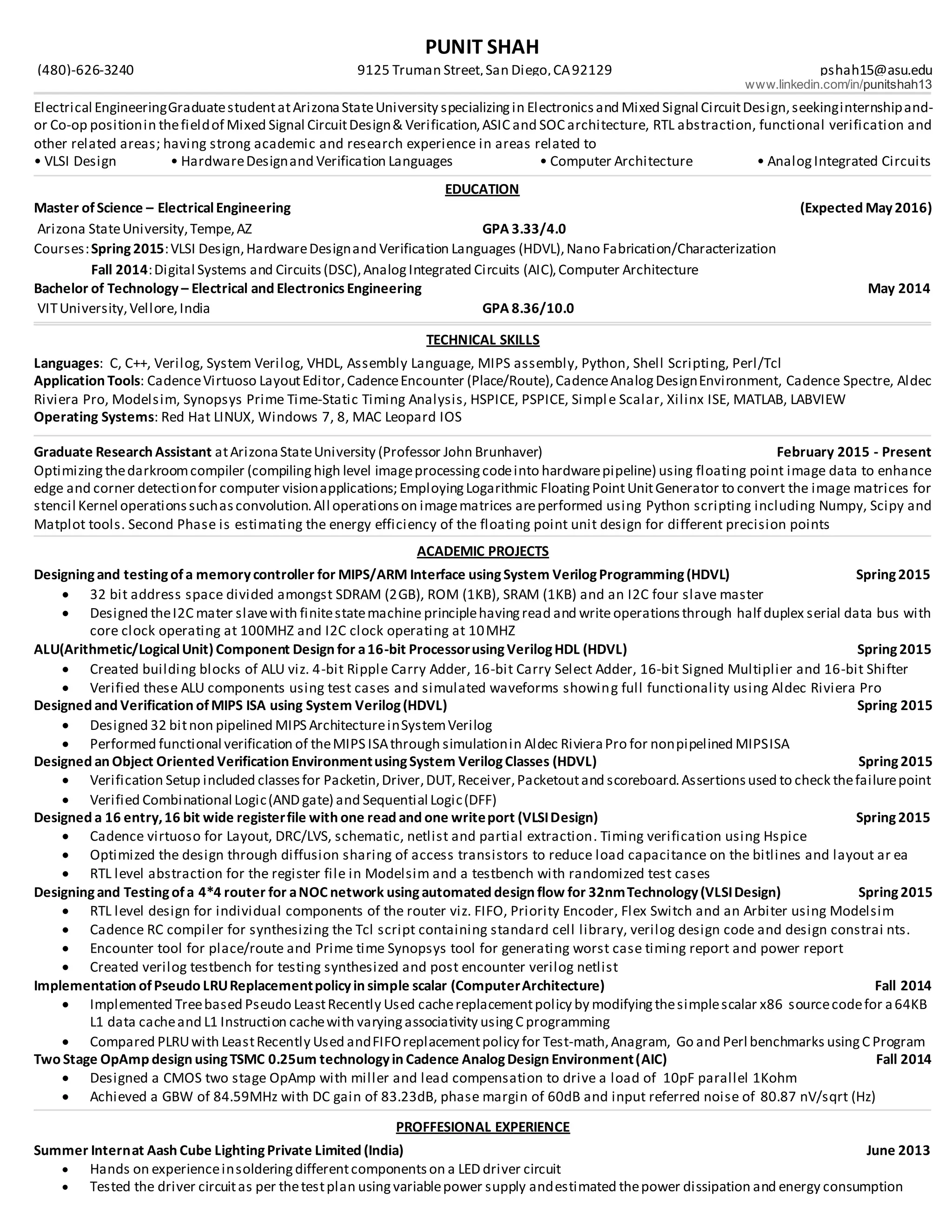

Punit Shah is a graduate student at Arizona State University seeking an internship or co-op position in mixed signal circuit design and verification. He has strong academic experience in areas such as VLSI design, hardware design verification, computer architecture, and analog integrated circuits. Some of his academic projects include designing a memory controller, ALU components, a MIPS processor, and a 4x4 router for a NOC network. He implemented a pseudo LRU cache replacement policy and designed a two-stage op-amp. He is currently optimizing a darkroom compiler to enhance edge detection for computer vision applications.