Ieee Vlsi Titles

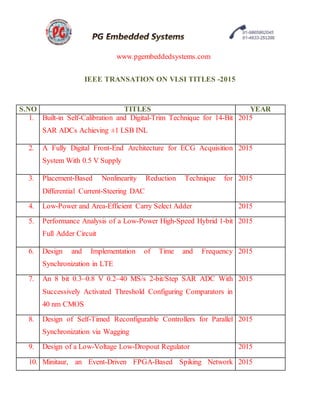

- 1. www.pgembeddedsystems.com IEEE TRANSATION ON VLSI TITLES -2015 S.NO TITLES YEAR 1. Built-in Self-Calibration and Digital-Trim Technique for 14-Bit SAR ADCs Achieving ±1 LSB INL 2015 2. A Fully Digital Front-End Architecture for ECG Acquisition System With 0.5 V Supply 2015 3. Placement-Based Nonlinearity Reduction Technique for Differential Current-Steering DAC 2015 4. Low-Power and Area-Efficient Carry Select Adder 2015 5. Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit 2015 6. Design and Implementation of Time and Frequency Synchronization in LTE 2015 7. An 8 bit 0.3–0.8 V 0.2–40 MS/s 2-bit/Step SAR ADC With Successively Activated Threshold Configuring Comparators in 40 nm CMOS 2015 8. Design of Self-Timed Reconfigurable Controllers for Parallel Synchronization via Wagging 2015 9. Design of a Low-Voltage Low-Dropout Regulator 2015 10. Minitaur, an Event-Driven FPGA-Based Spiking Network 2015

- 2. www.pgembeddedsystems.com Accelerator 11. Unipolar Logic Gates Based on Spatial Wave-Function Switched FETs 2015 12. Design of ultrahigh-speed low-voltage CMOS CML buffers and latches 2015 13. Asynchronous Domino Logic Pipeline Design Based on Constructed Critical Data Path 2015 14. An Inter/Intra-Chip Optical Network for Manycore Processors 2015 15. Per-Core DVFS With Switched-Capacitor Converters for Energy Efficiency in Manycore Processors 2015 16. Signal Processing With Direct Computations on Compressively Sensed Data 2015 17. Z-TCAM: An SRAM-based Architecture for TCAM 2015 18. A Low-Jitter Cell-Based Digitally Controlled Oscillator With Differential Multiphase Outputs 2015 19. All Digital Energy Sensing for Minimum Energy Tracking 2015 20. Novel Reconfigurable Hardware Architecture for Polynomial Matrix Multiplications 2015 21. A 65 nm Cryptographic Processor for High Speed Pairing Computation 2015

- 3. www.pgembeddedsystems.com 22. A Low-Latency and Low-Power Hybrid Scheme for On-Chip Networks 2015 23. Level-Converting Retention Flip-Flop for Reducing Standby Power in ZigBee SoCs 2015 24. Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2015 25. A New Efficiency-Improvement Low-Ripple Charge-Pump Boost Converter Using Adaptive Slope Generator With Hysteresis Voltage Comparison Techniques 2015 26. A Highly Efficient Ultralow Photovoltaic Power Harvesting System With MPPT for Internet of Things Smart Nodes 2015 27. A 0.325 V, 600-kHz, 40-nm 72-kb 9T Subthreshold SRAM with Aligned Boosted Write Wordline and Negative Write Bitline Write-Assist 2015 28. Reverse Converter Design via Parallel-Prefix Adders: Novel Components, Methodology, and Implementations 2015 29. Economizing TSV Resources in 3-D Network-on-Chip Design 2015 30. A 2.5-Gb/s DLL-Based Burst-Mode Clock and Data Recovery Circuit With Oversampling 2015 31. Low-Cost On-Chip Clock Jitter Measurement Scheme 2015 32. A Self-Powered High-Efficiency Rectifier With Automatic 2015

- 4. www.pgembeddedsystems.com Resetting of Transducer Capacitance in Piezoelectric Energy Harvesting Systems 33. An 11.5 Gb/s 1/4th Baud-Rate CTLE and Two-Tap DFE With Boosted High Frequency Gain in 110-nm CMOS 2015 34. Fault Tolerant Parallel Filters Based on Error Correction Codes 2015 35. A 16-mW 8-Bit 1-GS/s Digital-Subranging ADC in 55-nm CMOS 2015 36. Precise VLSI Architecture for AI Based 1-D/ 2-D Daub-6 Wavelet Filter Banks With Low Adder-Count 2015 37. Protein Alignment Systolic Array Throughput Optimization 2015 38. Runtime Thermal Management for 3-D Chip- Multiprocessors With Hybrid SRAM/MRAM L2 Cache 2015 39. A 16-mW 8-Bit 1-GS/s Digital-Subranging ADC in 55-nm CMOS 2015 40. A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal- Independent Delta-I Noise DfT Scheme 2015 41. A GPU-Accelerated Parallel Shooting Algorithm for Analysis of Radio Frequency and Microwave Integrated Circuits 2015 42. A Method for Improving Power Grid Resilience to Electromigration-Caused via Failures 2015 43. A Process-Variation Resilient Current Mode Logic With Simultaneous Regulations for Time Constant, Voltage 2015

- 5. www.pgembeddedsystems.com Swing, Level Shifting, and DC Gain Using Time-Reference- Based Adaptive Biasing Chain 44. A Synergetic Use of Bloom Filters for Error Detection and Correction 2015 45. Actively Alleviate Power Gating-InducedPower/Ground Noise Using Parasitic Capacitanceof On-Chip Memories in MPSoC 2015 46. An 8 bit 0.3–0.8 V 0.2–40 MS/s 2-bit/Step SAR ADC With Successively Activated Threshold Configuring Comparators in 40 nm CMOS 2015 47. An Accuracy-Adjustment Fixed-Width Booth Multiplier Based on Multilevel Conditional Probability 2015 48. Demonstrating HW–SW Transient Error Mitigationon the Single-Chip Cloud Computer Data Plane 2015 49. Design of Self-Timed Reconfigurable Controllers for Parallel Synchronization via Wagging 2015 50. Design Techniques to Improve Blocker Tolerance of Continuous-Time __ ADCs 2015 51. Effects of Intermittent Faults on the Reliability of a Reduced Instruction Set Computing (RISC) Microprocessor 2015 52. Efficient Hardware Architecture of ηTPairing Accelerator Over Characteristic Three 2015 53. Energy Efficiency Optimization Through Codesignof the 2015

- 6. www.pgembeddedsystems.com Transmitter and Receiver in High-Speed On-Chip Interconnects 54. Exploiting Same Tag Bits to Improve the Reliability of the Cache Memories 2015 55. Fast and Wide Range Voltage Conversion in Multisupply Voltage Designs 2015 56. Precise VLSI Architecture for AI Based 1-D/ 2-D Daub-6 Wavelet Filter Banks With Low Adder-Count 2015 57. Protein Alignment Systolic Array Throughput Optimization 2015 58. Runtime Thermal Management for 3-D Chip- Multiprocessors With Hybrid SRAM/MRAM L2 Cache 2015 59. A 16-mW 8-Bit 1-GS/s Digital-Subranging ADC in 55-nm CMOS 2015 60. A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal- Independent Delta-I Noise DfT Scheme 2015 61. A GPU-Accelerated Parallel Shooting Algorithm for Analysis of Radio Frequency and Microwave Integrated Circuits 2015 62. A Method for Improving Power Grid Resilience to Electromigration-Caused via Failures 2015 63. A Process-Variation Resilient Current Mode Logic With Simultaneous Regulations for Time Constant, Voltage Swing, Level Shifting, and DC Gain Using Time-Reference- Based Adaptive Biasing Chain 2015 64. A Synergetic Use of Bloom Filters for Error Detection and 2015

- 7. www.pgembeddedsystems.com Correction 65. Fast Design Optimization Through Simple KrigingMetamodeling: A Sense Amplifier Case Study 2015 66. Fast Radix-10 Multiplication Using Redundant BCD Codes 2015 67. Fat-Tree-Based Optical Interconnection Networks Under Crosstalk Noise Constraint 2015 68. Fault Tolerant Parallel Filters Based on Error Correction Codes 2015 69. Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications 2015 70. Functional Constraint Extraction From Register Transfer Level for ATPG 2015 71. Hardware Efficient Mixed Radix-25/16/9 FFT for LTE Systems 2015 72. Level-Converting Retention Flip-Flop for Reducing Standby Power in ZigBeeSoCs 2015 73. Low-Complexity Hardware Design for Fast Solving LSPs With Coordinated Polynomial Solution 2015 74. Low-Energy Two-Stage Algorithm for High Efficacy Epileptic Seizure Detection 2015 75. Parallel Thermal Analysis of 3-D Integrated Circuits With Liquid Cooling on CPU-GPU Platforms 2015 76. Protein Alignment Systolic Array Throughput Optimization 2015 77. Quaternary Logic Lookup Table in Standard CMOS 2015 78. Fast Design Optimization Through Simple 2015

- 8. www.pgembeddedsystems.com KrigingMetamodeling: A Sense Amplifier Case Study 79. Fast Radix-10 Multiplication Using Redundant BCD Codes 2015 80. Fat-Tree-Based Optical Interconnection Networks Under Crosstalk Noise Constraint 2015 81. Fault Tolerant Parallel Filters Based on Error Correction Codes 2015 82. Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications 2015 83. Functional Constraint Extraction From Register Transfer Level for ATPG 2015 84. Hardware Efficient Mixed Radix-25/16/9 FFT for LTE Systems 2015 85. Level-Converting Retention Flip-Flop for Reducing Standby Power in ZigBeeSoCs 2015 86. Low-Complexity Hardware Design for Fast Solving LSPs With Coordinated Polynomial Solution 2015 87. Low-Energy Two-Stage Algorithm for High Efficacy Epileptic Seizure Detection 2015 88. Parallel Thermal Analysis of 3-D Integrated Circuits With Liquid Cooling on CPU-GPU Platforms 2015 89. Protein Alignment Systolic Array Throughput Optimization 2015 90. Quaternary Logic Lookup Table in Standard CMOS 2015 91. Fast Design Optimization Through Simple KrigingMetamodeling: A Sense Amplifier Case Study 2015

- 9. www.pgembeddedsystems.com 92. Fast Radix-10 Multiplication Using Redundant BCD Codes 2015 93. Fat-Tree-Based Optical Interconnection Networks Under Crosstalk Noise Constraint 2015 94. Fault Tolerant Parallel Filters Based on Error Correction Codes 2015