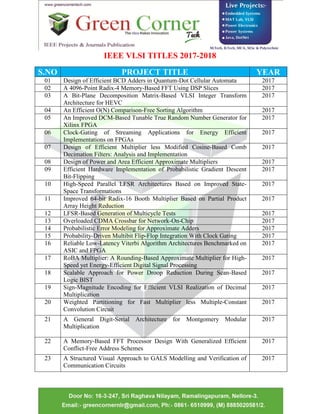

Vlsi titles 2017 18

- 1. IEEE VLSI TITLES 2017-2018 S.NO PROJECT TITLE YEAR 01 Design of Efficient BCD Adders in Quantum-Dot Cellular Automata 2017 02 A 4096-Point Radix-4 Memory-Based FFT Using DSP Slices 2017 03 A Bit-Plane Decomposition Matrix-Based VLSI Integer Transform Architecture for HEVC 2017 04 An Efficient O(N) Comparison-Free Sorting Algorithm 2017 05 An Improved DCM-Based Tunable True Random Number Generator for Xilinx FPGA 2017 06 Clock-Gating of Streaming Applications for Energy Efficient Implementations on FPGAs 2017 07 Design of Efficient Multiplier less Modified Cosine-Based Comb Decimation Filters: Analysis and Implementation 2017 08 Design of Power and Area Efficient Approximate Multipliers 2017 09 Efficient Hardware Implementation of Probabilistic Gradient Descent Bit-Flipping 2017 10 High-Speed Parallel LFSR Architectures Based on Improved State- Space Transformations 2017 11 Improved 64-bit Radix-16 Booth Multiplier Based on Partial Product Array Height Reduction 2017 12 LFSR-Based Generation of Multicycle Tests 2017 13 Overloaded CDMA Crossbar for Network-On-Chip 2017 14 Probabilistic Error Modeling for Approximate Adders 2017 15 Probability-Driven Multibit Flip-Flop Integration With Clock Gating 2017 16 Reliable Low-Latency Viterbi Algorithm Architectures Benchmarked on ASIC and FPGA 2017 17 RoBA Multiplier: A Rounding-Based Approximate Multiplier for High- Speed yet Energy-Efficient Digital Signal Processing 2017 18 Scalable Approach for Power Droop Reduction During Scan-Based Logic BIST 2017 19 Sign-Magnitude Encoding for Efficient VLSI Realization of Decimal Multiplication 2017 20 Weighted Partitioning for Fast Multiplier less Multiple-Constant Convolution Circuit 2017 21 A General Digit-Serial Architecture for Montgomery Modular Multiplication 2017 22 A Memory-Based FFT Processor Design With Generalized Efficient Conflict-Free Address Schemes 2017 23 A Structured Visual Approach to GALS Modelling and Verification of Communication Circuits 2017

- 2. 24 Area-Efficient Architecture for Dual-Mode Double Precision Floating Point Division 2017 25 Area-Time Efficient Architecture of FFT-Based Montgomery Multiplication 2017 26 Digit-Level Serial-In Parallel-Out Multiplier Using Redundant Representation for a Class of Finite Fields 2017 27 DLAU: A Scalable Deep Learning Accelerator Unit on FPGA 2017 28 Energy-Efficient VLSI Realization of Binary64 Division With Redundant Number Systems 2017 29 High-Throughput and Energy-Efficient Belief Propagation Polar Code Decoder 2017 30 LLR-Based Successive-Cancellation List Decoder for Polar Codes With Multi bit Decision 2017 31 Low-Latency, Low-Area, and Scalable Systolic-Like Modular Multipliers for GF(2m) Based on Irreducible All-One Polynomials 2017 32 On the VLSI Energy Complexity of LDPC Decoder Circuits 2017 33 Reconfigurable Constant Multiplication for FPGAs 2017 34 An Improved Design of a Reversible Fault Tolerant LUT-Based FPGA 2017 35 Flexible DSP Accelerator Architecture Exploiting Carry-Save Arithmetic 2017 36 A Method to Design Single Error Correction Codes With Fast Decoding for a Subset of Critical Bits 2016 37 A Mixed-Decimation MDF Architecture for Radix-2k Parallel FFT 2016 38 A Modified Partial Product Generator for Redundant Binary Multipliers 2016 39 Design & Analysis of 16 bit RISC Processor Using low Power Pipelining 2016 40 Design and Analysis of Inexact Floating-Point Adders 2016 41 Design Methodology for Voltage-Scaled Clock Distribution Networks 2016 42 Design of Carry Select Adder for Low-Power and High Speed VLSI Applications 2016 43 Floating-Point Butterfly Architecture Based on Binary Signed-Digit Representation 2016 44 High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels 2016 45 Hybrid LUT/Multiplexer FPGA Logic Architectures 2016

- 3. 46 Implementation of A High Speed Multiplier for High-Performance and Low Power Applications 2016 47 Low-Power and Area-Efficient Shift Register Using Pulsed Latches 2016 48 Low-Power FPGA Design Using Memoization-Based Approximate Computing 2016 49 Memory-Reduced Turbo Decoding Architecture Using NII Metric Compression 2016 50 High performance pipelined Architecture of elliptic curve scaller multiplication over GF(2m) 2016 51 Digital multiplierless realization of two coupled biological hindmarsh- Rose Neuron model 2016 52 Multiple constant multiplication algorithm for high speed and low power design 2016 53 VLSI Design for Convolutive Blind Source Separation 2016 54 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2015 55 In-Field Test for Permanent Faults in FIFO Buffers of NoC Routers 2015 56 On-Chip Codeword Generation to Cope With Crosstalk 2014 57 4-2 Compressor Design with New XOR-XNOR Module[Back End] 2014 58 Z-TCAM: An SRAM-based Architecture for TCAM 2014 59 High Throughput Architecture for the Advanced Encryption Standard Algorithm 2014 60 An Optimized Modified Booth Recoder for Efficient Design of the Add- Multiply Operator 2014 61 Design and estimation of delay, power and area for Parallel prefix Adders 2014 62 Area–Delay–Power Efficient Carry-Select Adder 2014 63 Design of High Performance 64 bit MAC Unit 2014 64 Low voltage dual mode logic: Model analysis and parameter extraction 2013 65 A High Speed Low Power CAM With a Parity Bit and Power-Gated ML Sensing 2013 66 Design and Implementation of an On-Chip Permutation Network for Multiprocessor System-On-Chip 2013 67 Low-Power Dual Dynamic Node Pulsed Hybrid Flip-Flop Featuring Efficient Embedded Logic 2013 68 Least Complex S-Box and Its Fault Detection for Robust Advanced Encryption Standard Algorithm 2013 69 Novel method of digital clock frequency multiplication and division using floating point arithmetic 2013 70 A High Speed Binary Floating Point Multiplier Using Dadda Algorithm 2013 71 An FPGA Based High Speed IEEE-754 Double Precision Floating Point Multiplier U sing Verilog 2013 72 Design and Implementation of 32 Bit Unsigned Multiplier Using CLAA and CSLA 2013

- 4. 73 VLSI Implementation of a High Speed Single Precision Floating Point Unit Using Verilog 2013 74 VLSI Implementation of a Low-Cost High-Quality Image Scaling Processor 2013 75 RTL Design and VLSI Implementation of an efficient Convolutional Encoder and Adaptive Viterbi Decoder 2013 76 Design of Low Logical Cost Conservative Reversible Adders using Novel PCTG 2013 77 Reliable and Higher Throughput Anti-Collision Technique for RFID UHF Tag 2012 78 Accumulator Based 3-Weight Pattern Generation 2012 79 Design and Characterization of Parallel Prefix Adders using FPGAs 2011 80 Self-Immunity Technique to Improve Register File Integrity against Soft Errors 2011 81 High Throughput DA-Based DCT With High Accuracy Error- Compensated Adder Tree 2011 82 High Speed ASIC Design of Complex Multiplier Using Vedic Mathematics 2011 83 Low-Power and Area-Efficient Carry Select Adder 2011 84 Vlsi Architecture Of Parallel Multiplier–Accumulator Based On Radix-2 Modified Booth Algorithm 2011 85 Design and Characterization of Parallel Prefix Adders using FPGAs IEEE 86 Implementation of a Self-Motivated Arbitration Scheme for the Multi- Layer AHB Bus matrix IEEE 87 An Efficient Architecture for 3-D Discrete Wavelet Transform IEEE 88 High Speed VLSI Architecture for General Linear Feedback Shift Register (LFSR) Structures IEEE 89 Self-Immunity Technique to Improve Register File Integrity against Soft Errors IEEE