VHDL Implementation of Flexible Multiband Divider

•

1 like•425 views

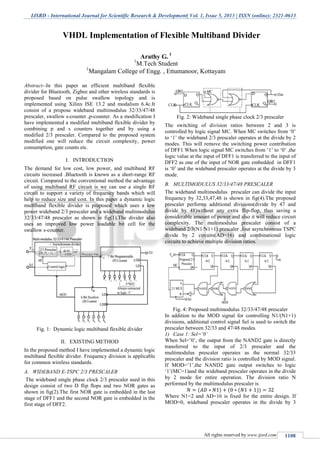

In this paper an efficient multiband flexible divider for Bluetooth, Zigbee and other wireless standards is proposed based on pulse swallow topology and is implemented using Xilinx ISE 13.2 and modalism 6.4c.It consist of a propose wideband multimodulus 32/33/47/48 prescaler, swallow s-counter ,p-counter. As a modification I have implemented a modified multiband flexible divider by combining p and s counters together and by using a modified 2/3 prescaler. Compared to the proposed system modified one will reduce the circuit complexity, power consumption, gate counts etc.

Report

Share

Report

Share

Download to read offline

Recommended

A Single-Phase Clock Multiband Low-Power Flexible Divider

In this paper, a low-power single-phase clock multiband flexible divider for Bluetooth, Zigbee, and IEEE 802.15.4 and 802.11 a/b/g WLAN frequency synthesizers The frequency synthesizer was implemented using a charge-pump based phase-locked loop with a tri-state phase/frequency detector and a programmable pulse-swallow frequency divider. Since the required frequency of operation can be as high as 1.4GHz, the speed of the digital logic used in the frequency divider is a critical design factor. A custom library of digital logic gates was designed using MOS current-mode logic (MCML). These gates were designed to operate at frequencies up to 1.4GHz. This report outlines the design of the phase/frequency detector and the programmable pulse-swallow frequency divider. The design, layout, and simulation of the MCML logic family are also presented.

Analysis of switching and matching stubs in reconfigurable power divider with...

In this paper, performance analysis of switching and matching stubs was done to a reconfigurable power divider with Single Pole Double Throw (SPDT) switch function. Two designs (Design A and Design B) with different positions of switches and matching stubs were proposed. Rogers RO4350 (er=3.48, h=0.508 mm) was used in this analysis as a substrate material with copper thickness of 0.035 mm. The performance analysis was carried out based on insertion loss, return loss and isolation parameters. The simulated results showed that Design B had a better performance than Design A and was able to work as a reconfigurable power divider with SPDT switch function.

J42046469

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For Hig...

This paper presents a new topology to implement MOS current mod logic (MCML) tri-state buffers. In Mos current mode logic (MCML) current section is improves the performance and maintains low power of the circuit. MCML circuits contains true differential operation by which provides the feature of low noise level generation and static power dissipation. So the amount of current drawn from the power supply does not depends on the switching activity. Due to this MOS current mode logic (MCML) circuits have been useful for developing analog and mixed signal IC’s. The implementing of MCML D-flip flop and Frequency divider done by using MCML D-latches. The proposed MCML D-latch consumes less power as it makes use of low power tri-state buffers. Which promotes power saving due to reduction in the overall current flow in the proposed D flip flop topology is verified though Cadence GPDK-180nM CMOS technology parameters.

Welcome to International Journal of Engineering Research and Development (IJERD)

journal publishing, how to publish research paper, Call For research paper, international journal, publishing a paper, IJERD, journal of science and technology, how to get a research paper published, publishing a paper, publishing of journal, publishing of research paper, reserach and review articles, IJERD Journal, How to publish your research paper, publish research paper, open access engineering journal, Engineering journal, Mathemetics journal, Physics journal, Chemistry journal, Computer Engineering, Computer Science journal, how to submit your paper, peer reviw journal, indexed journal, reserach and review articles, engineering journal, www.ijerd.com, research journals,

yahoo journals, bing journals, International Journal of Engineering Research and Development, google journals, hard copy of journal

Design of all digital phase locked loop

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Design of subthreshold dml logic gates with power gating techniques

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Recommended

A Single-Phase Clock Multiband Low-Power Flexible Divider

In this paper, a low-power single-phase clock multiband flexible divider for Bluetooth, Zigbee, and IEEE 802.15.4 and 802.11 a/b/g WLAN frequency synthesizers The frequency synthesizer was implemented using a charge-pump based phase-locked loop with a tri-state phase/frequency detector and a programmable pulse-swallow frequency divider. Since the required frequency of operation can be as high as 1.4GHz, the speed of the digital logic used in the frequency divider is a critical design factor. A custom library of digital logic gates was designed using MOS current-mode logic (MCML). These gates were designed to operate at frequencies up to 1.4GHz. This report outlines the design of the phase/frequency detector and the programmable pulse-swallow frequency divider. The design, layout, and simulation of the MCML logic family are also presented.

Analysis of switching and matching stubs in reconfigurable power divider with...

In this paper, performance analysis of switching and matching stubs was done to a reconfigurable power divider with Single Pole Double Throw (SPDT) switch function. Two designs (Design A and Design B) with different positions of switches and matching stubs were proposed. Rogers RO4350 (er=3.48, h=0.508 mm) was used in this analysis as a substrate material with copper thickness of 0.035 mm. The performance analysis was carried out based on insertion loss, return loss and isolation parameters. The simulated results showed that Design B had a better performance than Design A and was able to work as a reconfigurable power divider with SPDT switch function.

J42046469

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For Hig...

This paper presents a new topology to implement MOS current mod logic (MCML) tri-state buffers. In Mos current mode logic (MCML) current section is improves the performance and maintains low power of the circuit. MCML circuits contains true differential operation by which provides the feature of low noise level generation and static power dissipation. So the amount of current drawn from the power supply does not depends on the switching activity. Due to this MOS current mode logic (MCML) circuits have been useful for developing analog and mixed signal IC’s. The implementing of MCML D-flip flop and Frequency divider done by using MCML D-latches. The proposed MCML D-latch consumes less power as it makes use of low power tri-state buffers. Which promotes power saving due to reduction in the overall current flow in the proposed D flip flop topology is verified though Cadence GPDK-180nM CMOS technology parameters.

Welcome to International Journal of Engineering Research and Development (IJERD)

journal publishing, how to publish research paper, Call For research paper, international journal, publishing a paper, IJERD, journal of science and technology, how to get a research paper published, publishing a paper, publishing of journal, publishing of research paper, reserach and review articles, IJERD Journal, How to publish your research paper, publish research paper, open access engineering journal, Engineering journal, Mathemetics journal, Physics journal, Chemistry journal, Computer Engineering, Computer Science journal, how to submit your paper, peer reviw journal, indexed journal, reserach and review articles, engineering journal, www.ijerd.com, research journals,

yahoo journals, bing journals, International Journal of Engineering Research and Development, google journals, hard copy of journal

Design of all digital phase locked loop

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Design of subthreshold dml logic gates with power gating techniques

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Design of low power cmos logic circuits using gate diffusion input (gdi) tech...

The Gate diffusion input (GDI) is a novel technique

for low power digital circuit design. This techniq

ue

reduces the power dissipation, propagation delay, a

rea of digital circuits and it maintains low comple

xity

of logic design. In this paper, the 4×1 Multiplexer

, 8×3 Encoder, BCD Counter and Mealy State Machine

were implemented by using Pass Transistors (PT), Tr

ansmission Gate (TG) and Gate Diffusion Input (GDI)

technique and then they were compared with each oth

er for power dissipation. The Multiplexers and

Encoders are combinational circuits and Counters an

d mealy machines are sequential circuits both of th

em

are very important digital systems so power optimiz

ation should be done to those digital circuits. The

whole processes for development of digital circuits

and simulation was done by using the mentor graphi

cs

backend tool. This method can also be extended to t

he processors and other high level designs for

optimization of power dissipation, area and delay i

n order to increase the circuit efficiency.

Ad4103173176

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

Abstract The attempt made in the paper shows an innovative designing for the enhancement and reliability in CMOS technology. A 2.4 GHz resistive feedback narrowband noise amplifier (LNA) using a series inductor input matching networks. It is easy reliable with an extra gm boosting as well as inductively degenerated topology. By using this resistive feedback topology increases the gain as well as noise figure of 2.2 dB,S21 parameter of 26dB,and IIP3 of -13dBm,while 2.8mW of power consuming from a 1.2V and its area 0.6mm2 in 0.13μm CMOS ,which gives the best figure of merit and performance. Keywords: LNA, CMOS, noise figure, resistive feedback, gm boosting, voltage gain boosting.

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...eSAT Publishing House

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and TechnologyCw35552557

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Minimization of redundant internal voltage swing in cmos full adder

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

ASIC DESIGN OF MINI-STEREO DIGITAL AUDIO PROCESSOR UNDER SMIC 180NM TECHNOLOGY

ASIC DESIGN OF MINI-STEREO DIGITAL AUDIO PROCESSOR UNDER SMIC 180NM TECHNOLOGYIlango Jeyasubramanian

- Designed and analyzed a complete MSDAP with optimized convolution computation by only shifts and adds using power-of-2 coefficients. Synthesized the chip through high level architecture design (C Program), Logic synthesis (Synopsys Design Compiler) and Physical Synthesis (Synopsys IC compiler).

- Achieved a low power consumption of 3.1438mW at 29.186Mhz clock frequency, with core utilization of 70% and chip area of 1.29mm2.Design and implementation of 15 4 compressor using 1-bit semi domino full add...

Abstract In this paper, we present 15-4 Compressor for Digital signal processing. A new Low power full adder and 5-3 compressor are used in this 15-4 compressor. Full Adder and 5:3 compressors are realized by Semi Domino logic which is faster and consumes less power than other conventional logics. Objective of this Work is to inspect the power, delay, power delay product of full adders in different logic styles and to inspect power, delay, and power delay product of Semi domino 5-3 compressor architecture with other architectures. Simulation results demonstrate the superiority of the proposed adder circuit against the pre-proposed adder circuits in terms of power, delay, PDP. The proposed style gets its benefit in terms of power, delay, PDP. The performance of the adder circuits and compressors is based on TSMC 28nm CMOS process models at the supply voltage of 1V, 500MHz frequency evaluated by the comparing of the simulation results obtained from Cadence spectre. Keywords: Semi Domino Logic, Full adder, 5-3 compressor, power, delay, PDP, TSMC 28nm.

Customizable Microprocessor design on Nexys 3 Spartan FPGA Board

- Designed a 4 stage pipelined, 16-bit customizable microprocessor in VHDL which can execute instructions (direct & memory mapped addressing modes), handle interrupts (IVT based), communicate with IO devices including keyboard and VGA monitor and facilitates with a single port BLOCK RAM for Stack, Instruction , Data & IVT memory. Keyboard and VGA controller provides input-output interface gives user flexibility of keying in the instructions through Keyboard that is interfaced with Nexys 3 through USB 2.0; VGA interface to display the output. Keyboard and VGA controllers are also coded in VHDL.

- Implemented the VHDL code on Nexys 3 Spartan FPGA board which involved simulation, synthesis and bit file generation using Xilinx ISE,programming the FPGA with Digilent Adept.

- Employed the debug mode to make the design more user friendly

IRJET - Low Power M-Sequence Code Generator using LFSR for Body Sensor No...

https://www.irjet.net/archives/V7/i4/IRJET-V7I4213.pdf

High speed customized serial protocol for IP integration on FPGA based SOC ap...

International Journal of Modern Engineering Research (IJMER) is Peer reviewed, online Journal. It serves as an international archival forum of scholarly research related to engineering and science education.

International Journal of Modern Engineering Research (IJMER) covers all the fields of engineering and science: Electrical Engineering, Mechanical Engineering, Civil Engineering, Chemical Engineering, Computer Engineering, Agricultural Engineering, Aerospace Engineering, Thermodynamics, Structural Engineering, Control Engineering, Robotics, Mechatronics, Fluid Mechanics, Nanotechnology, Simulators, Web-based Learning, Remote Laboratories, Engineering Design Methods, Education Research, Students' Satisfaction and Motivation, Global Projects, and Assessment…. And many more.

The Analysis of Dead Time on Switching Loss in High and Low Side MOSFETs of Z...

This work is about the analysis of dead time variation

on switching losses in a Zero Voltage Switching (ZVS)

synchronous buck converter (SBC) circuit. In high frequency

converter circuits, switching losses are commonly linked with

high and low side switches of SBC circuit. They are activated

externally by the gate driver circuit. The duty ratio, dead time

and resonant inductor are the parameters that affect the

efficiency of the circuit. These variables can be adjusted for

the optimization purposes. The study primarily focuses on

varying the settings of input pulses of the MOSFETs in the

resonant gate driver circuit which consequently affects the

performance of the ZVS synchronous buck converter circuit.

Using the predetermined inductor of 9 nH, the frequency is

maintained at 1 MHz for each cycle transition. The switching

loss graph is obtained and switching losses for both S1 and S2

are calculated and compared to the findings from previous

work. It has shown a decrease in losses by 13.8 % in S1. A dead

time of 15 ns has been determined to be optimized value in

the SBC design.

Df34655661

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Efficient reconfigurable architecture of baseband

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

More Related Content

What's hot

Design of low power cmos logic circuits using gate diffusion input (gdi) tech...

The Gate diffusion input (GDI) is a novel technique

for low power digital circuit design. This techniq

ue

reduces the power dissipation, propagation delay, a

rea of digital circuits and it maintains low comple

xity

of logic design. In this paper, the 4×1 Multiplexer

, 8×3 Encoder, BCD Counter and Mealy State Machine

were implemented by using Pass Transistors (PT), Tr

ansmission Gate (TG) and Gate Diffusion Input (GDI)

technique and then they were compared with each oth

er for power dissipation. The Multiplexers and

Encoders are combinational circuits and Counters an

d mealy machines are sequential circuits both of th

em

are very important digital systems so power optimiz

ation should be done to those digital circuits. The

whole processes for development of digital circuits

and simulation was done by using the mentor graphi

cs

backend tool. This method can also be extended to t

he processors and other high level designs for

optimization of power dissipation, area and delay i

n order to increase the circuit efficiency.

Ad4103173176

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

Abstract The attempt made in the paper shows an innovative designing for the enhancement and reliability in CMOS technology. A 2.4 GHz resistive feedback narrowband noise amplifier (LNA) using a series inductor input matching networks. It is easy reliable with an extra gm boosting as well as inductively degenerated topology. By using this resistive feedback topology increases the gain as well as noise figure of 2.2 dB,S21 parameter of 26dB,and IIP3 of -13dBm,while 2.8mW of power consuming from a 1.2V and its area 0.6mm2 in 0.13μm CMOS ,which gives the best figure of merit and performance. Keywords: LNA, CMOS, noise figure, resistive feedback, gm boosting, voltage gain boosting.

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...eSAT Publishing House

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and TechnologyCw35552557

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Minimization of redundant internal voltage swing in cmos full adder

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

ASIC DESIGN OF MINI-STEREO DIGITAL AUDIO PROCESSOR UNDER SMIC 180NM TECHNOLOGY

ASIC DESIGN OF MINI-STEREO DIGITAL AUDIO PROCESSOR UNDER SMIC 180NM TECHNOLOGYIlango Jeyasubramanian

- Designed and analyzed a complete MSDAP with optimized convolution computation by only shifts and adds using power-of-2 coefficients. Synthesized the chip through high level architecture design (C Program), Logic synthesis (Synopsys Design Compiler) and Physical Synthesis (Synopsys IC compiler).

- Achieved a low power consumption of 3.1438mW at 29.186Mhz clock frequency, with core utilization of 70% and chip area of 1.29mm2.Design and implementation of 15 4 compressor using 1-bit semi domino full add...

Abstract In this paper, we present 15-4 Compressor for Digital signal processing. A new Low power full adder and 5-3 compressor are used in this 15-4 compressor. Full Adder and 5:3 compressors are realized by Semi Domino logic which is faster and consumes less power than other conventional logics. Objective of this Work is to inspect the power, delay, power delay product of full adders in different logic styles and to inspect power, delay, and power delay product of Semi domino 5-3 compressor architecture with other architectures. Simulation results demonstrate the superiority of the proposed adder circuit against the pre-proposed adder circuits in terms of power, delay, PDP. The proposed style gets its benefit in terms of power, delay, PDP. The performance of the adder circuits and compressors is based on TSMC 28nm CMOS process models at the supply voltage of 1V, 500MHz frequency evaluated by the comparing of the simulation results obtained from Cadence spectre. Keywords: Semi Domino Logic, Full adder, 5-3 compressor, power, delay, PDP, TSMC 28nm.

Customizable Microprocessor design on Nexys 3 Spartan FPGA Board

- Designed a 4 stage pipelined, 16-bit customizable microprocessor in VHDL which can execute instructions (direct & memory mapped addressing modes), handle interrupts (IVT based), communicate with IO devices including keyboard and VGA monitor and facilitates with a single port BLOCK RAM for Stack, Instruction , Data & IVT memory. Keyboard and VGA controller provides input-output interface gives user flexibility of keying in the instructions through Keyboard that is interfaced with Nexys 3 through USB 2.0; VGA interface to display the output. Keyboard and VGA controllers are also coded in VHDL.

- Implemented the VHDL code on Nexys 3 Spartan FPGA board which involved simulation, synthesis and bit file generation using Xilinx ISE,programming the FPGA with Digilent Adept.

- Employed the debug mode to make the design more user friendly

IRJET - Low Power M-Sequence Code Generator using LFSR for Body Sensor No...

https://www.irjet.net/archives/V7/i4/IRJET-V7I4213.pdf

High speed customized serial protocol for IP integration on FPGA based SOC ap...

International Journal of Modern Engineering Research (IJMER) is Peer reviewed, online Journal. It serves as an international archival forum of scholarly research related to engineering and science education.

International Journal of Modern Engineering Research (IJMER) covers all the fields of engineering and science: Electrical Engineering, Mechanical Engineering, Civil Engineering, Chemical Engineering, Computer Engineering, Agricultural Engineering, Aerospace Engineering, Thermodynamics, Structural Engineering, Control Engineering, Robotics, Mechatronics, Fluid Mechanics, Nanotechnology, Simulators, Web-based Learning, Remote Laboratories, Engineering Design Methods, Education Research, Students' Satisfaction and Motivation, Global Projects, and Assessment…. And many more.

The Analysis of Dead Time on Switching Loss in High and Low Side MOSFETs of Z...

This work is about the analysis of dead time variation

on switching losses in a Zero Voltage Switching (ZVS)

synchronous buck converter (SBC) circuit. In high frequency

converter circuits, switching losses are commonly linked with

high and low side switches of SBC circuit. They are activated

externally by the gate driver circuit. The duty ratio, dead time

and resonant inductor are the parameters that affect the

efficiency of the circuit. These variables can be adjusted for

the optimization purposes. The study primarily focuses on

varying the settings of input pulses of the MOSFETs in the

resonant gate driver circuit which consequently affects the

performance of the ZVS synchronous buck converter circuit.

Using the predetermined inductor of 9 nH, the frequency is

maintained at 1 MHz for each cycle transition. The switching

loss graph is obtained and switching losses for both S1 and S2

are calculated and compared to the findings from previous

work. It has shown a decrease in losses by 13.8 % in S1. A dead

time of 15 ns has been determined to be optimized value in

the SBC design.

Df34655661

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Efficient reconfigurable architecture of baseband

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

What's hot (20)

Design of low power cmos logic circuits using gate diffusion input (gdi) tech...

Design of low power cmos logic circuits using gate diffusion input (gdi) tech...

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

A 2.4 ghz cmos lna input matching design using resistive feedback topology in...

Minimization of redundant internal voltage swing in cmos full adder

Minimization of redundant internal voltage swing in cmos full adder

ASIC DESIGN OF MINI-STEREO DIGITAL AUDIO PROCESSOR UNDER SMIC 180NM TECHNOLOGY

ASIC DESIGN OF MINI-STEREO DIGITAL AUDIO PROCESSOR UNDER SMIC 180NM TECHNOLOGY

Design and implementation of 15 4 compressor using 1-bit semi domino full add...

Design and implementation of 15 4 compressor using 1-bit semi domino full add...

Customizable Microprocessor design on Nexys 3 Spartan FPGA Board

Customizable Microprocessor design on Nexys 3 Spartan FPGA Board

IRJET - Low Power M-Sequence Code Generator using LFSR for Body Sensor No...

IRJET - Low Power M-Sequence Code Generator using LFSR for Body Sensor No...

High speed customized serial protocol for IP integration on FPGA based SOC ap...

High speed customized serial protocol for IP integration on FPGA based SOC ap...

The Analysis of Dead Time on Switching Loss in High and Low Side MOSFETs of Z...

The Analysis of Dead Time on Switching Loss in High and Low Side MOSFETs of Z...

Viewers also liked

enhancement of low power pulse triggered flip-flop design based on signal fee...

Abstract: Low Power research major concern in today’s VLSI word. Practically, clocking system like flip-flop (FF) consumes large portion of total chip power. So in this paper we discuss about the design of the clock system using novel Flip-Flop design. In this paper, a novel low-power pulse-triggered flip-flop (FF) design is presented. Pulse- triggered FF (P-FF) has been considered as a popular alternative to the conventional master –slave based F. a low-power flip-flop (FF) design featuring an explicit type pulse-triggered structure and a modified true single phase clock latch based on a signal feed-through scheme is presented. The proposed design successfully solves the long discharging path problem in conventional explicit type pulse-triggered FF (P-FF) designs and achieves better speed and power performance in the applications of high speed. These circuits are simulated using Tanner Tools with TSMC018 technology.

Keywords: pulse-triggered flip-flop (FF), true single phase clock latch, clocking system

A High Speed Wallace Tree Multiplier Using Modified Booth Algorithm for Fast ...

Abstract— Designing multipliers that are of high-speed, low power, and regular in layout are of substantial research interest. Speed of the multiplier can be increased by reducing the generated partial products. Many attempts have been made to reduce the number of partial products generated in a multiplication process; one of them is Wallace tree multiplier. Wallace Tree CSA structures have been used to sum the partial products in reduced time. In this paper Wallace tree construction is investigated and evaluated. Speed of traditional Wallace tree multiplier can be improved by using compressor techniques. In this paper Wallace tree is constructed by traditional method and with the help of compressor techniques such as 4:2 compressor, 5:2 compressor, 6:2 compressor, 7:2 compressor. Therefore, minimizing the number of half adders used in a multiplier reduction will reduce the complexity.

Index Terms—Component, formatting, style, styling, insert. (key words)

Booths algorithm for Multiplication

Booths algorithm for Multiplication with flowchart for easy understanding with explained suitable examples.

Wallace tree multiplier.pptx1

it consist of comparison between both wallace tree and array tree multiplier

Viewers also liked (9)

enhancement of low power pulse triggered flip-flop design based on signal fee...

enhancement of low power pulse triggered flip-flop design based on signal fee...

A High Speed Wallace Tree Multiplier Using Modified Booth Algorithm for Fast ...

A High Speed Wallace Tree Multiplier Using Modified Booth Algorithm for Fast ...

Similar to VHDL Implementation of Flexible Multiband Divider

Is3515091514

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Implementation of High Speed OFDM Transceiver using FPGA

Abstract - Proficient, multi mode and re-configurable architecture of interleaver/de-interleaver for multiple standards, like DVB, OFDM and WLAN is presented. Interleaver plays vital role in 4G technologies to recover symbols from burst errors. The aim of our work is to design a reconfigurable modulation technique called Adaptive modulation scheme uses QAM, QPSK and BPSK modulation that adapt themselves based on channel Signal to Noise ratio. Subcarrier allocation algorithm specifically used to focus on utilizing channels with high gains. Our proposed model can achieves a data rate of min 2.5 Gbps as per 3GPP standard by adaptive modulation technique using QAM, BPSK and QPSK.

Analysis of Women Harassment inVillages Using CETD Matrix Modal

Abstract-It is commonly understood that misbehavior intends to upset .Law says ,the repeated intentional misbehavior towards women is an offensive. The main concept of this paper can find something interesting that will make us reflect on what is done by women’s rights and gender equality. To solve such problem, in this paper we are interested to adopt CETD matrix.

First order sigma delta modulator with low-power consumption implemented in a...

Abstract

This paper presents a design of a switched-capacitor discrete time 1st order Delta-Sigma modulator used for a resolution of 8 bits

Sigma-Delta analog to digital converter. For lower power consumption, the use of operational transconductance amplifier is

necessary in order to provide wide output voltage swing and moderate DC gain. Simulation results showed that with 0.35um CMOS

technology, 80 KHz signal bandwidth and oversampling rate of 64, the modulator achieved 49.25 dB Signal to Noise Ratio (SNR) and

the power consumption was 5.5 mW under ±1.5V supply voltage .

Index terms: Analog-to-Digital conversion, Delta-Sigma modulation, CMOS technology, Transconductance operational

amplifier.

First order sigma delta modulator with low-power

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology.

Design of all digital phase locked loop (d pll) with fast acquisition time

Abstract

A Digital PLL is designed with improved acquisition time and power efficiency. The implemented D-PLL can operate

from 6.54MHz to 105MHz with a power dissipation of is 7.763μW (at 210MHz) with 1.2V supply voltage. The D-PLL is

synthesized using cadence RTL compiler in 45nm CMOS process technology.

Keywords: Digital PLL, Digital Phase/Frequency detector, NCO, Divide by N counter.

Fpga based low power and high performance address

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Fpga based low power and high performance address generator for wimax deinter...

Abstract

The main aim of this project is to generate the address generation circuitry of Deinterleaver used in the WiMAX transreceiver using

the Xilinx Field Programmable Gate Array(FPGA). The floor function associated with the implementation of FPGA is very difficult in

IEEE 802.16e standard. So we eliminate the requirement of floor function by using a simple mathematical algorithm. Some

modulations like QPSK, 16-QAM and 64-QAM along with its code rates make our approach to be novel and high efficient.

Keywords— Modulation circuits, Deinterleaver/Interleaver circuit, Wireless SYSTEMS

Efficient reconfigurable architecture of baseband demodulator in sdr

Abstract This paper presents the simulation architecture and performance analysis with the use of ZCD technic. A Zero-Crossing based All-Digital Baseband Demodulation architecture is proposed in this work. This architecture supports demodulation of all modulation schemes including MSK, PSK, FSK, and QAM. The proposed structure is very low area, low power, and low latency and can operate in real-time. Moreover it can switch, in run-time, between multiple modulation schemes like GMSK (GSM), QPSK (CDMA), GFSK (Bluetooth), 8-PSK (EDGE), Offset-QPSK (W-CDMA), etc. In addition, the phase resolution of the demodulator is scalable with performance. In addition, bit-wise amplitude quantization based quad-decomposition approach is utilized to demodulate higher order M-ary QAM modulations such as 16-QAM & 64-QAM, which is also a highly scalable architecture. This structure of demodulator provides energy-efficient and resource-efficient implementation of various wireless standards in physical layer of SDR. Keywords — Physical layer, Mobile and Wireless Communication, Software Defined radio (SDR), Zero Cross Detection (ZCD), Modulation Schemes, Architecture, high level synthesis, FPGA.

Ek35775781

International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research and review articles in the fields of Computer Science, Neural Networks, Electrical Engineering, Software Engineering, Information Technology, Mechanical Engineering, Chemical Engineering, Plastic Engineering, Food Technology, Textile Engineering, Nano Technology & science, Power Electronics, Electronics & Communication Engineering, Computational mathematics, Image processing, Civil Engineering, Structural Engineering, Environmental Engineering, VLSI Testing & Low Power VLSI Design etc.

Low power and high performance detff using common feedback inverter logic

Abstract The power consumption of a system is crucial parameter in modern VLSI circuits especially for low power applications. In this project, a low power Double Edge Triggered D-Flip Flop (DETFF) design is proposed in 65nm CMOS technology. The proposed DETFF is having less number of transistors than earlier designs. Simulations are carried out using HSPICE tool with different clock frequencies ranging from 400MHz to 2GHz and with different supply voltages ranging from 0.8V to 1.2V. In general, a power delay product (PDP)-based comparison is appropriate for low power portable systems. At nominal condition, the PDP of the proposed DETFF is improved by 65.48% and 44.85% over earlier designs DETFF1 and DETFF2 respectively. Simulation results show lowest power dissipation and least delay than existing designs, which claims that the proposed DETFF is suitable for low power and high speed applications. Keywords: CMOS, flip-flops, Double-edge triggered, power dissipation, delay and PDP.

A low complexity distributed differential scheme based on orthogonal space t...

This work proposes a new differential cooperative diversity scheme with high data rate and low decoding complexity using the decode-and-forward protocol. The proposed model does not require either differential encoding or channel state information at the source node, relay nodes, or destination node where the data sequence is directly transmitted and the differential detection method is applied at the relay nodes and the destination node. The proposed technique enjoys a low encoding and decoding complexity at the source node, the relay nodes, and the destination node. Furthermore, the performance of the proposed strategy is analyzed by computer simulations in quasi-static Rayleigh fading channel and using the decode-and-forward protocol. The simulation results show that the proposed differential technique outperforms the corresponding reference strategies.

Spur Reduction Of MB-OFDM UWB System using CMOS Frequency Synthesizer

As Technology progress deeper into submicron

CMOS, traditional analog circuits face problems that are

not to be solved purely by analog innovations. Instead,

new architectures are being proposed which take advantages

of the relatively cheaper of the digital circuits to augment or

improve the diminishing performance of the analog

circuitry. The conventional approach performs the design of

14 bands CMOS frequency synthesizers with spur reduction

for MB-OFMD for analog circuits which have high

distortions and noise. My proposed work is to replace the

analog input PLL into All Digital PLL with spur reduction.

Then the frequency mixing architecture alleviates

harmonics mixing and pulling to diminish spur

generation. The simulation is performed using Model SIM

and the implementation using Microwind to diminish spur

reduction.

Extremely Low Power FIR Filter for a Smart Dust Sensor Module

Digital filters are common components in many applications today, also in for sensor systems, such as large-scale distributed smart dust sensors. For these applications the power consumption is very critical, it has to be extremely low. With the transistor technology scaling becoming more and more sensitive to e.g. gate leakage, it has become a necessity to find ways to minimize the flow of leakage in current CMOS logic. This paper studies sub-threshold source coupled logic (STSCL) in a 45-nm process. The STSCL can be used instead of traditional CMOS to meet the low power and energy consumption requirements. The STSCL style is in this paper used to design a digital filter, applicable for the audio interface of a smart dust sensor where the sample frequency will be 44.1 kHz. A finite-length impulse response (FIR) filter is used with transposed direct form structure and for the coefficient multiplication five-bit canonic signed digit [7] based serial/parallel multipliers were used. The power consumption is calculated along with the delay in order to present the power delay product (PDP) such that the performance of the sub-threshold logic can be compared with corresponding CMOS implementation. The simulated results shows a significant reduction in energy consumption (in terms of PDP) with the system running at a supply voltage as low as 0.2 V using STSCL.

Optimization of Digitally Controlled Oscillator with Low Power

IOSR journal of VLSI and Signal Processing (IOSRJVSP) is a double blind peer reviewed International Journal that publishes articles which contribute new results in all areas of VLSI Design & Signal Processing. The goal of this journal is to bring together researchers and practitioners from academia and industry to focus on advanced VLSI Design & Signal Processing concepts and establishing new collaborations in these areas.

Design and realization of microelectronic systems using VLSI/ULSI technologies require close collaboration among scientists and engineers in the fields of systems architecture, logic and circuit design, chips and wafer fabrication, packaging, testing and systems applications. Generation of specifications, design and verification must be performed at all abstraction levels, including the system, register-transfer, logic, circuit, transistor and process levels

Similar to VHDL Implementation of Flexible Multiband Divider (20)

Implementation of High Speed OFDM Transceiver using FPGA

Implementation of High Speed OFDM Transceiver using FPGA

Analysis of Women Harassment inVillages Using CETD Matrix Modal

Analysis of Women Harassment inVillages Using CETD Matrix Modal

First order sigma delta modulator with low-power consumption implemented in a...

First order sigma delta modulator with low-power consumption implemented in a...

Design of all digital phase locked loop (d pll) with fast acquisition time

Design of all digital phase locked loop (d pll) with fast acquisition time

Fpga based low power and high performance address generator for wimax deinter...

Fpga based low power and high performance address generator for wimax deinter...

Efficient reconfigurable architecture of baseband demodulator in sdr

Efficient reconfigurable architecture of baseband demodulator in sdr

Low power and high performance detff using common feedback inverter logic

Low power and high performance detff using common feedback inverter logic

A low complexity distributed differential scheme based on orthogonal space t...

A low complexity distributed differential scheme based on orthogonal space t...

Spur Reduction Of MB-OFDM UWB System using CMOS Frequency Synthesizer

Spur Reduction Of MB-OFDM UWB System using CMOS Frequency Synthesizer

Extremely Low Power FIR Filter for a Smart Dust Sensor Module

Extremely Low Power FIR Filter for a Smart Dust Sensor Module

Optimization of Digitally Controlled Oscillator with Low Power

Optimization of Digitally Controlled Oscillator with Low Power

More from ijsrd.com

IoT Enabled Smart Grid

Due to availability of internet and evolution of embedded devices, Internet of things can be useful to contribute in energy domain. The Internet of Things (IoT) will deliver a smarter grid to enable more information and connectivity throughout the infrastructure and to homes. Through the IoT, consumers, manufacturers and utility providers will come across new ways to manage devices and ultimately conserve resources and save money by using smart meters, home gateways, smart plugs and connected appliances. The future smart home, various devices will be able to measure and share their energy consumption, and actively participate in house-wide or building wide energy management systems. This paper discusses the different approaches being taken worldwide to connect the smart grid. Full system solutions can be developed by combining hardware and software to address some of the challenges in building a smarter and more connected smart grid.

A Survey Report on : Security & Challenges in Internet of Things

In the era of computing technology, Internet of Things (IoT) devices are now popular in each and every domains like e-governance, e-Health, e-Home, e-Commerce, and e-Trafficking etc. Iot is spreading from small to large applications in all fields like Smart Cities, Smart Grids, Smart Transportation. As on one side IoT provide facilities and services for the society. On the other hand, IoT security is also a crucial issues.IoT security is an area which totally concerned for giving security to connected devices and networks in the IoT .As, IoT is vast area with usability, performance, security, and reliability as a major challenges in it. The growth of the IoT is exponentially increases as driven by market pressures, which proportionally increases the security threats involved in IoT The relationship between the security and billions of devices connecting to the Internet cannot be described with existing mathematical methods. In this paper, we explore the opportunities possible in the IoT with security threats and challenges associated with it.

IoT for Everyday Life

In today’s emerging world of Internet, each and every thing is supposed to be in connected mode with the help of billions of smart devices. By connecting all the devises used in our day to day life, make our life trouble less and easy. We are incorporated in a world where we are used to have smart phones, smart cars, smart gadgets, smart homes and smart cities. Different institutes and researchers are working for creating a smart world for us but real question which we need to emphasis on is how to make dumb devises talk with uncommon hardware and communication technology. For the same what kind of mechanism to use with various protocols and less human interaction. The purpose is to provide the key area for application of IoT and a platform on which various devices having different mechanism and protocols can communicate with an integrated architecture.

Study on Issues in Managing and Protecting Data of IOT

This paper discusses variety of issues for preserving and managing data produced by IoT. Every second large amount of data are added or updated in the IoT databases across the heterogeneous environment. While managing the data each phase of data processing for IoT data is exigent like storing data, querying, indexing, transaction management and failure handling. We also refer to the problem of data integration and protection as data requires to be fit in single layout and travel securely as they arrive in the pool from diversified sources in different structure. Finally, we confer a standardized pathway to manage and to defend data in consistent manner.

Interactive Technologies for Improving Quality of Education to Build Collabor...

Today with advancement in Information Communication Technology (ICT) the way the education is being delivered is seeing a paradigm shift from boring classroom lectures to interactive applications such as 2-D and 3-D learning content, animations, live videos, response systems, interactive panels, education games, virtual laboratories and collaborative research (data gathering and analysis) etc. Engineering is emerging with more innovative solutions in the field of education and bringing out their innovative products to improve education delivery. The academic institutes which were once hesitant to use such technology are now looking forward to such innovations. They are adopting the new ways as they are realizing the vast benefits of using such methods and technology. The benefits are better comprehensibility, improved learning efficiency of students, and access to vast knowledge resources, geographical reach, quick feedback, accountability and quality research. This paper focuses on how engineering can leverage the latest technology and build a collaborative learning environment which can then be integrated with the national e-learning grid.

Internet of Things - Paradigm Shift of Future Internet Application for Specia...

In the world more than 15% people are living with disability that also include children below age of 10 years. Due to lack of independent support services specially abled (handicap) people overly rely on other people for their basic needs, that excludes them from being financially and socially active. The Internet of Things (IoT) can give support system and a better quality of life as well as participation in routine and day to day life. For this purpose, the future solutions for current problems has been introduced in this paper. Daunting challenges have been considered as future research and glimpse of the IoT for specially abled person is given in the paper.

A Study of the Adverse Effects of IoT on Student's Life

Internet of things (IoT) is the most powerful invention and if used in the positive direction, internet can prove to be very productive. But, now a days, due to the social networking sites such as Face book, WhatsApp, twitter, hike etc. internet is producing adverse effects on the student life, especially those students studying at college Level. As it is rightly said, something which has some positive effects also has some of the negative effects on the other hand. In this article, we are discussing some adverse effects of IoT on student’s life.

Pedagogy for Effective use of ICT in English Language Learning

The use of information and communications technology (ICT) in education is a relatively new phenomenon and it has been the educational researchers' focus of attention for more than two decades. Educators and researchers examine the challenges of using ICT and think of new ways to integrate ICT into the curriculum. However, there are some barriers for the teachers that prevent them to use ICT in the classroom and develop supporting materials through ICT. The purpose of this study is to examine the high school English teachers’ perceptions of the factors discouraging teachers to use ICT in the classroom.

Virtual Eye - Smart Traffic Navigation System

In recent years usage of private vehicles create urban traffic more and more crowded. As result traffic becomes one of the important problems in big cities in all over the world. Some of the traffic concerns are traffic jam and accidents which have caused a huge waste of time, more fuel consumption and more pollution. Time is very important parameter in routine life. The main problem faced by the people is real time routing. Our solution Virtual Eye will provide the current updates as in the real time scenario of the specific route. This research paper presents smart traffic navigation system, based on Internet of Things, which is featured by low cost, high compatibility, easy to upgrade, to replace traditional traffic management system and the proposed system can improve road traffic tremendously.

Ontological Model of Educational Programs in Computer Science (Bachelor and M...

In this work there is illustrated an ontological model of educational programs in computer science for bachelor and master degrees in Computer science and for master educational program “Computer science as second competence†by Tempus project PROMIS.

Understanding IoT Management for Smart Refrigerator

Lately the concept of Internet of Things (IoT) is being more elaborated and devices and databases are proposed thereby to meet the need of an Internet of Things scenario. IoT is being considered to be an integral part of smart house where devices will be connected to each other and also react upon certain environmental input. This will eventually include the home refrigerator, air conditioner, lights, heater and such other home appliances. Therefore, we focus our research on the database part for such an IoT’ fridge which we called as smart Fridge. We describe the potentials achievable through a database for an IoT refrigerator to manage the refrigerator food and also aid the creation of a monthly budget of the house for a family. The paper aims at the data management issue based on a proposed design for an intelligent refrigerator leveraging the sensor technology and the wireless communication technology. The refrigerator which identifies products by reading the barcodes or RFID tags is proposed to order the required products by connecting to the Internet. Thus the goal of this paper is to minimize human interaction to maintain the daily life events.

DESIGN AND ANALYSIS OF DOUBLE WISHBONE SUSPENSION SYSTEM USING FINITE ELEMENT...

Double wishbone designs allow the engineer to carefully control the motion of the wheel throughout suspension travel. 3-D model of the Lower Wishbone Arm is prepared by using CAD software for modal and stress analysis. The forces and moments are used as the boundary conditions for finite element model of the wishbone arm. By using these boundary conditions static analysis is carried out. Then making the load as a function of time; quasi-static analysis of the wishbone arm is carried out. A finite element based optimization is used to optimize the design of lower wishbone arm. Topology optimization and material optimization techniques are used to optimize lower wishbone arm design.

A Review: Microwave Energy for materials processing

Microwave energy is a latest largest growing technique for material processing. This paper presents a review of microwave technologies used for material processing and its use for industrial applications. Advantages in using microwave energy for processing material include rapid heating, high heating efficiency, heating uniformity and clean energy. The microwave heating has various characteristics and due to which it has been become popular for heating low temperature applications to high temperature applications. In recent years this novel technique has been successfully utilized for the processing of metallic materials. Many researchers have reported microwave energy for sintering, joining and cladding of metallic materials. The aim of this paper is to show the use of microwave energy not only for non-metallic materials but also the metallic materials. The ability to process metals with microwave could assist in the manufacturing of high performance metal parts desired in many industries, for example in automotive and aeronautical industries.

Web Usage Mining: A Survey on User's Navigation Pattern from Web Logs

With an expontial growth of World Wide Web, there are so many information overloaded and it became hard to find out data according to need. Web usage mining is a part of web mining, which deal with automatic discovery of user navigation pattern from web log. This paper presents an overview of web mining and also provide navigation pattern from classification and clustering algorithm for web usage mining. Web usage mining contain three important task namely data preprocessing, pattern discovery and pattern analysis based on discovered pattern. And also contain the comparative study of web mining techniques.

APPLICATION OF STATCOM to IMPROVED DYNAMIC PERFORMANCE OF POWER SYSTEM

Application of FACTS controller called Static Synchronous Compensator STATCOM to improve the performance of power grid with Wind Farms is investigated .The essential feature of the STATCOM is that it has the ability to absorb or inject fastly the reactive power with power grid . Therefore the voltage regulation of the power grid with STATCOM FACTS device is achieved. Moreover restoring the stability of the power system having wind farm after occurring severe disturbance such as faults or wind farm mechanical power variation is obtained with STATCOM controller . The dynamic model of the power system having wind farm controlled by proposed STATCOM is developed . To validate the powerful of the STATCOM FACTS controller, the studied power system is simulated and subjected to different severe disturbances. The results prove the effectiveness of the proposed STATCOM controller in terms of fast damping the power system oscillations and restoring the power system stability.

Making model of dual axis solar tracking with Maximum Power Point Tracking

Now a days solar harvesting is more popular. As the popularity become higher the material quality and solar tracking methods are more improved. There are several factors affecting the solar system. Major influence on solar cell, intensity of source radiation and storage techniques The materials used in solar cell manufacturing limit the efficiency of solar cell. This makes it particularly difficult to make considerable improvements in the performance of the cell, and hence restricts the efficiency of the overall collection process. Therefore, the most attainable maximum power point tracking method of improving the performance of solar power collection is to increase the mean intensity of radiation received from the source used. The purposed of tracking system controls elevation and orientation angles of solar panels such that the panels always maintain perpendicular to the sunlight. The measured variables of our automatic system were compared with those of a fixed angle PV system. As a result of the experiment, the voltage generated by the proposed tracking system has an overall of about 28.11% more than the fixed angle PV system. There are three major approaches for maximizing power extraction in medium and large scale systems. They are sun tracking, maximum power point (MPP) tracking or both.

A REVIEW PAPER ON PERFORMANCE AND EMISSION TEST OF 4 STROKE DIESEL ENGINE USI...

In day today's relevance, it is mandatory to device the usage of diesel in an economic way. In present scenario, the very low combustion efficiency of CI engine leads to poor performance of engine and produces emission due to incomplete combustion. Study of research papers is focused on the improvement in efficiency of the engine and reduction in emissions by adding ethanol in a diesel with different blends like 5%, 10%, 15%, 20%, 25% and 30% by volume. The performance and emission characteristics of the engine are tested observed using blended fuels and comparative assessment is done with the performance and emission characteristics of engine using pure diesel.

Study and Review on Various Current Comparators

This paper presents study and review on various current comparators. It also describes low voltage current comparator using flipped voltage follower (FVF) to obtain the single supply voltage. This circuit has short propagation delay and occupies a small chip area as compare to other current comparators. The results of this circuit has obtained using PSpice simulator for 0.18 μm CMOS technology and a comparison has been performed with its non FVF counterpart to contrast its effectiveness, simplicity, compactness and low power consumption.

Reducing Silicon Real Estate and Switching Activity Using Low Power Test Patt...

Power dissipation is a challenging problem for today's system-on-chip design and test. This paper presents a novel architecture which generates the test patterns with reduced switching activities; it has the advantage of low test power and low hardware overhead. The proposed LP-TPG (test pattern generator) structure consists of modified low power linear feedback shift register (LP-LFSR), m-bit counter, gray counter, NOR-gate structure and XOR-array. The seed generated from LP-LFSR is EXCLUSIVE-OR ed with the data generated from gray code generator. The XOR result of the sequence is single input changing (SIC) sequence, in turn reduces the switching activity and so power dissipation will be very less. The proposed architecture is simulated using Modelsim and synthesized using Xilinx ISE9.2.The Xilinx chip scope tool will be used to test the logic running on FPGA.

Defending Reactive Jammers in WSN using a Trigger Identification Service.

In the last decade, the greatest threat to the wireless sensor network has been Reactive Jamming Attack because it is difficult to be disclosed and defend as well as due to its mass destruction to legitimate sensor communications. As discussed above about the Reactive Jammers Nodes, a new scheme to deactivate them efficiently is by identifying all trigger nodes, where transmissions invoke the jammer nodes, which has been proposed and developed. Due to this identification mechanism, many existing reactive jamming defending schemes can be benefited. This Trigger Identification can also work as an application layer .In this paper, on one side we provide the several optimization problems to provide complete trigger identification service framework for unreliable wireless sensor networks and on the other side we also provide an improved algorithm with regard to two sophisticated jamming models, in order to enhance its robustness for various network scenarios.

More from ijsrd.com (20)

A Survey Report on : Security & Challenges in Internet of Things

A Survey Report on : Security & Challenges in Internet of Things

Study on Issues in Managing and Protecting Data of IOT

Study on Issues in Managing and Protecting Data of IOT

Interactive Technologies for Improving Quality of Education to Build Collabor...

Interactive Technologies for Improving Quality of Education to Build Collabor...

Internet of Things - Paradigm Shift of Future Internet Application for Specia...

Internet of Things - Paradigm Shift of Future Internet Application for Specia...

A Study of the Adverse Effects of IoT on Student's Life

A Study of the Adverse Effects of IoT on Student's Life

Pedagogy for Effective use of ICT in English Language Learning

Pedagogy for Effective use of ICT in English Language Learning

Ontological Model of Educational Programs in Computer Science (Bachelor and M...

Ontological Model of Educational Programs in Computer Science (Bachelor and M...

Understanding IoT Management for Smart Refrigerator

Understanding IoT Management for Smart Refrigerator

DESIGN AND ANALYSIS OF DOUBLE WISHBONE SUSPENSION SYSTEM USING FINITE ELEMENT...

DESIGN AND ANALYSIS OF DOUBLE WISHBONE SUSPENSION SYSTEM USING FINITE ELEMENT...

A Review: Microwave Energy for materials processing

A Review: Microwave Energy for materials processing

Web Usage Mining: A Survey on User's Navigation Pattern from Web Logs

Web Usage Mining: A Survey on User's Navigation Pattern from Web Logs

APPLICATION OF STATCOM to IMPROVED DYNAMIC PERFORMANCE OF POWER SYSTEM

APPLICATION OF STATCOM to IMPROVED DYNAMIC PERFORMANCE OF POWER SYSTEM

Making model of dual axis solar tracking with Maximum Power Point Tracking

Making model of dual axis solar tracking with Maximum Power Point Tracking

A REVIEW PAPER ON PERFORMANCE AND EMISSION TEST OF 4 STROKE DIESEL ENGINE USI...

A REVIEW PAPER ON PERFORMANCE AND EMISSION TEST OF 4 STROKE DIESEL ENGINE USI...

Reducing Silicon Real Estate and Switching Activity Using Low Power Test Patt...

Reducing Silicon Real Estate and Switching Activity Using Low Power Test Patt...

Defending Reactive Jammers in WSN using a Trigger Identification Service.

Defending Reactive Jammers in WSN using a Trigger Identification Service.

Recently uploaded

Architectural Portfolio Sean Lockwood

This portfolio contains selected projects I completed during my undergraduate studies. 2018 - 2023

Runway Orientation Based on the Wind Rose Diagram.pptx

Runway Orientation Based on the Wind Rose Diagram

WATER CRISIS and its solutions-pptx 1234

Water scarcity is the lack of fresh water resources to meet the standard water demand. There are two type of water scarcity. One is physical. The other is economic water scarcity.

Immunizing Image Classifiers Against Localized Adversary Attacks

This paper addresses the vulnerability of deep learning models, particularly convolutional neural networks

(CNN)s, to adversarial attacks and presents a proactive training technique designed to counter them. We

introduce a novel volumization algorithm, which transforms 2D images into 3D volumetric representations.

When combined with 3D convolution and deep curriculum learning optimization (CLO), itsignificantly improves

the immunity of models against localized universal attacks by up to 40%. We evaluate our proposed approach

using contemporary CNN architectures and the modified Canadian Institute for Advanced Research (CIFAR-10

and CIFAR-100) and ImageNet Large Scale Visual Recognition Challenge (ILSVRC12) datasets, showcasing

accuracy improvements over previous techniques. The results indicate that the combination of the volumetric

input and curriculum learning holds significant promise for mitigating adversarial attacks without necessitating

adversary training.

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Dynamic Programming

Backtracking

Techniques for Graphs

Branch and Bound

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdfWater Industry Process Automation & Control

Welcome to WIPAC Monthly the magazine brought to you by the LinkedIn Group Water Industry Process Automation & Control.

In this month's edition, along with this month's industry news to celebrate the 13 years since the group was created we have articles including

A case study of the used of Advanced Process Control at the Wastewater Treatment works at Lleida in Spain

A look back on an article on smart wastewater networks in order to see how the industry has measured up in the interim around the adoption of Digital Transformation in the Water Industry.Investor-Presentation-Q1FY2024 investor presentation document.pptx

this is the investor presemtaiton document for qurrter 1 2024

Hierarchical Digital Twin of a Naval Power System

A hierarchical digital twin of a Naval DC power system has been developed and experimentally verified. Similar to other state-of-the-art digital twins, this technology creates a digital replica of the physical system executed in real-time or faster, which can modify hardware controls. However, its advantage stems from distributing computational efforts by utilizing a hierarchical structure composed of lower-level digital twin blocks and a higher-level system digital twin. Each digital twin block is associated with a physical subsystem of the hardware and communicates with a singular system digital twin, which creates a system-level response. By extracting information from each level of the hierarchy, power system controls of the hardware were reconfigured autonomously. This hierarchical digital twin development offers several advantages over other digital twins, particularly in the field of naval power systems. The hierarchical structure allows for greater computational efficiency and scalability while the ability to autonomously reconfigure hardware controls offers increased flexibility and responsiveness. The hierarchical decomposition and models utilized were well aligned with the physical twin, as indicated by the maximum deviations between the developed digital twin hierarchy and the hardware.

Top 10 Oil and Gas Projects in Saudi Arabia 2024.pdf

Saudi Arabia stands as a titan in the global energy landscape, renowned for its abundant oil and gas resources. It's the largest exporter of petroleum and holds some of the world's most significant reserves. Let's delve into the top 10 oil and gas projects shaping Saudi Arabia's energy future in 2024.

Final project report on grocery store management system..pdf

In today’s fast-changing business environment, it’s extremely important to be able to respond to client needs in the most effective and timely manner. If your customers wish to see your business online and have instant access to your products or services.

Online Grocery Store is an e-commerce website, which retails various grocery products. This project allows viewing various products available enables registered users to purchase desired products instantly using Paytm, UPI payment processor (Instant Pay) and also can place order by using Cash on Delivery (Pay Later) option. This project provides an easy access to Administrators and Managers to view orders placed using Pay Later and Instant Pay options.

In order to develop an e-commerce website, a number of Technologies must be studied and understood. These include multi-tiered architecture, server and client-side scripting techniques, implementation technologies, programming language (such as PHP, HTML, CSS, JavaScript) and MySQL relational databases. This is a project with the objective to develop a basic website where a consumer is provided with a shopping cart website and also to know about the technologies used to develop such a website.