An03 dws

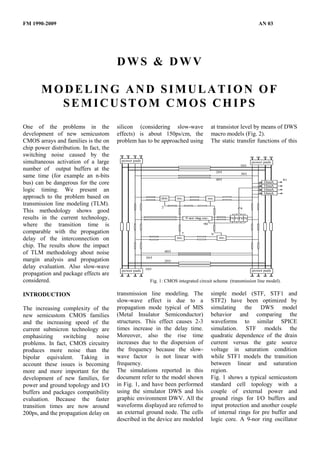

- 1. FM 1990-2009 AN 03 DWS & DWV MODELING AND SIMULATION OF SEMICUSTOM CMOS CHIPS One of the problems in the silicon (considering slow-wave at transistor level by means of DWS development of new semicustom effects) is about 150ps/cm, the macro models (Fig. 2). CMOS arrays and families is the on problem has to be approached using The static transfer functions of this chip power distribution. In fact, the switching noise caused by the simultaneous activation of a large power pads power pads 101 number of output buffers at the 201 301 same time (for example an n-bits 401 81 bus) can be dangerous for the core 16mA 16mA logic timing. We present an 16mA 16mA approach to the problem based on driv. rec. rec. transmission line modeling (TLM). 2 4 This methodology shows good results in the current technology, 9 nor ring osc. IVIVIVIV where the transition time is 90 comparable with the propagation 7 9 delay of the interconnection on rec. rec. chip. The results show the impact 403 of TLM methodology about noise 303 margin analysis and propagation 203 delay evaluation. Also slow-wave 103 power pads power pads propagation and package effects are considered. Fig. 1: CMOS integrated circuit scheme (transmission line model). INTRODUCTION transmission line modeling. The simple model (STF, STF1 and slow-wave effect is due to a STF2) have been optimized by The increasing complexity of the propagation mode typical of MIS simulating the DWS model new semicustom CMOS families (Metal Insulator Semiconductor) behavior and comparing the and the increasing speed of the structures. This effect causes 2-3 waveforms to similar SPICE current submicron technology are times increase in the delay time. simulation. STF models the emphasizing switching noise Moreover, also the rise time quadratic dependence of the drain problems. In fact, CMOS circuitry increases due to the dispersion of current versus the gate source produces more noise than the the frequency because the slow- voltage in saturation condition bipolar equivalent. Taking in wave factor is not linear with while STF1 models the transition account these issues is becoming frequency. between linear and saturation more and more important for the The simulations reported in this region. development of new families, for document refer to the model shown Fig. 1 shows a typical semicustom power and ground topology and I/O in Fig. 1, and have been performed standard cell topology with a buffers and packages compatibility using the simulator DWS and his couple of external power and evaluation. Because the faster graphic environment DWV. All the ground rings for I/O buffers and transition times are now around waveforms displayed are referred to input protection and another couple 200ps, and the propagation delay on an external ground node. The cells of internal rings for pre buffer and described in the device are modeled logic core. A 9-nor ring oscillator

- 2. D Cgs b) two couples of effect has been noted, due to the VDD and GND common interconnection through G pads used at the package. STF TD1 TD2 STF 2 Cds opposite corner The simulations show the voltage Vgs of the chip; transients on both power and c) four couples ground rings probed at two opposite Cgs STF1 of VDD and corners of the chip. Fig. 3a shows Vds GND pads used, that it is possible to have different one for each values of the power ( V 0.3V) at corner of the the same time and different chip. locations due to noise wave A double propagation within the rings. This Ids k k1 bonding has been effect decreases with the increasing S considered for of the pads number for power and N_channel Vgs Vds k*Ids both VDD and ground on chip and their uniform GND signals. For distribution around the chip STF STF1 STF2 double bonding boundary. Ids k k1 is intended a Due to the ring structure of power normal procedure and ground distribution, and the P_channel Vgs Vds k*Ids sometimes used periodic occurrence of the noise in the definition stimulus, some areas on the chip are STF STF1 STF2 of the bonding noisier than others, due to noise diagram wave interference. This stationary Fig. 2: Example of macro model structure for MOS transistor with (connection chip- behavior depends on noise the p-channel and n-channel static transfer function. package) in order frequency, on time constants to reduce the presented by the power ring operating at about 40 MHz is used number of package pins dedicated distribution and power pads as core noise generator. Four 16mA for power and ground. Using this location (that cause bus drivers (with 50pF external procedure, two different power discontinuities). It is interesting to load) are used as I/O switching pads on chip, related to internal and note that, for this particular case, noise generator. external power ring pads, are the configuration b) shows less All the internal connections are bonded to the same package cavity peak-to-peak noise than the modeled by means of transmission pin. As result, the two power configuration c). lines, as well as the package pins (a distributions for logic core and PGA has been modeled in this output buffers are decoupled on OUTPUT WAVEFORMS case). chip but a not-negligible coupling A first level of clock tree distribution is used to evaluate the effects of the noise caused by the 7.00 V V(101) simultaneous switching of the 6.10 V V(201) peripheral output drivers on the V(103) 7.00 V internal signals (in the logic core) 5.20 V V(203) V(81) chip_1.g in terms of skew on jitter. 6.00 V 4.30 V V(81) 5.00 V chip_2.g POWER AND GROUND 3.40 V V(81) 4.00 V SIMULTANEOUS SWITCHING chip_4.g NOISE WITHIN THE CHIP 2.50 V 3.00 V 1.60 V 2.00 V Fig. 3 shows the simulated power and ground noise for the following 0.70 V 1.00 V power distribution topology: 0.00 V -0.20 V a) only a couple of VDD and GND pads used; -1.10 V -1.00 V a b -2.00 V -2.00 V c 200.00 -3.00 V 210.00 220.00 230.00 240.00 250.00 260.00 270.00 280.00 290.00 300.00 300.00 310.00 320.00 330.00 340.00 350.00 360.00 370.00 380.00 390.00 400.00 TIME[nS] TIME[nS] Fig. 3a: Power & ground voltage noise (1 P&G couple) Fig. 4: Output driver voltage (a=1 P&G couple, b=2 P&G couples, c=4 P&G couples)

- 3. 7.00 V V(101) V(201) 6.10 V V(103) 5.20 V V(203) An internal clock signal (Fig. 6a 4.30 V and 6b) has been analyzed at the 3.40 V driver output and at the input of 2.50 V two far receivers; the signals are displayed using eye-diagrams. It 1.60 V is possible to see that the 0.70 V propagation shows about 1ns of delay, 500ps of skew between the -0.20 V receiving taps and 500ps of jitter -1.10 V due to simultaneous switching -2.00 V noise. Simulations performed 200.00 210.00 220.00 230.00 240.00 250.00 260.00 270.00 280.00 290.00 300.00 using the RC (lumped or TIME[nS] distributed) model for the same Fig. 3b: Power & ground voltage noise (2 P&G couples) clock tree interconnection showed a delay evaluation which Due to the ground bouncing effects and GND package pins for I/O and is 30% lower than the result the output signals present an logic core. It is possible to note the obtained using TLM models. overshoot and undershoot of about noise shape and level differences on 2 V (Fig. 4). Increasing the number internal power and ground rings CONCLUSION of power pads, the slew-rate (nodes 301 and 401) for the two increases, so that the signals show configurations. In particular, in the The increasing speed of semicustom IC technologies leads 7.00 V V(101) to a growing impact on system V(201) performance of on-chip signal 6.10 V V(103) integrity issues related to both V(203) 5.20 V signal interconnection and power 4.30 V bouncing effects. Accurate models of interconnecting paths are needed 3.40 V in order to get reliable results from 2.50 V simulations and choose the best on- 1.60 V chip interconnect structure. TLM 0.70 V for both lossy slow-wave interconnect and for package -0.20 V effects is needed. This in turn -1.10 V requires the use of next generation -2.00 V simulation tools which are able to 200.00 210.00 220.00 230.00 240.00 250.00 260.00 270.00 280.00 290.00 300.00 deal with a large number of TIME[nS] transmission lines at very small Fig. 3c: Power & ground voltage noise (4 P&G couples) time-step (in the range of 5ps for CMOS technology). In this way the IC designer can more noise (no slew-rate control first case, the noise is mainly quickly evaluate several design has been assumed for the buffers correlated to the noise source in the alternatives for power supply, used). core. signal interconnections and The signal V(90) is the ring packaging issues. Transmission line BONDING AND INTERNAL oscillator output and it is shown as propagation on both signal and NOISE reference for noise correlation of noise paths frequently leads to ring bounces. difficult to predict or unexpected Fig. 5 shows the differences effects that can have a major impact between a chip supplied by double CLOCK SKEW AND NOISE on choosing the internal chip bonded pads (first four MARGIN EVALUATION architecture. simulations), or independent VDD

- 4. 1.16 V V(101) -1.14 V chip_2.g 6.10 V V(201) 3.96 V chip_2.g 1.14 V V(301) -1.12 V chip_2.g 5.88 V V(401) 3.94 V chip_2.g 1.41 V V(101) -1.18 V chip_2_spt.g 6.10 V V(201) 3.71 V chip_2_spt.g 0.91 V V(301) -1.17 V chip_2_spt.g 5.97 V V(401) 4.21 V chip_2_spt.g 5.59 V V(90) -0.75 V chip_2.g 100.00 130.00 160.00 190.00 220.00 250.00 280.00 310.00 340.00 370.00 400.00 TIME[nS] Fig. 5: Power and ground noise with double or single bonding 6.00 V V(2) -1.00 V 6.00 V V(7) -1.00 V 6.00 V V(9) -1.00 V 110.00 112.00 114.00 116.00 118.00 120.00 122.00 124.00 126.00 128.00 130.00 TIME[nS] Fig. 6a: Internal clock signal: eye diagrams (2 P&G couples, single bonding) 5.75 V V(2) -0.82 V 5.73 V V(7) -0.76 V 5.69 V V(9) -0.72 V 110.00 112.00 114.00 116.00 118.00 120.00 122.00 124.00 126.00 128.00 130.00 TIME[nS] Fig. 6b: Internal clock signal: eye diagrams (2 P&G couples, double bonding)