2015年8月19日 ディープラーニングセミナー2015

名古屋ルーセントタワー

エヌビディア合同会社 シニアデベロッパーテクノロジー エンジニア 成瀬彰

[概要]

本講演では、モルフォが取り組むDeep Learning(以下、DL)ビジネスについての概要と、実用化に 向けてディープラーニングではGPU利用がデファクトになっていますが、GPUを使うとなぜディープラーニングの学習フェーズを加速できるのか、その技術的な背景・理由を説明するとともに、エヌビディアのディープラーニング関連ソフトウェアの最新情報を紹介致します。

![CNN: Convolution Neural Network

フルコネクション (全結合層) cuBLAS

コンボリューション (畳み込み層) cuDNN

LeNet5 [LeCun et al.,1998]](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-17-320.jpg)

![全結合層

x[N] y[M]

w[N][M]

𝑦 𝑖 = 𝐹

𝑗

(𝑤 𝑖 𝑗 × 𝑥 𝑗 )](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-20-320.jpg)

![全結合層

x[N] y[M]

w[N][M]

x =

w[N][M] x[N] y[M]

行列 ベクトル

𝑦 𝑖 = 𝐹

𝑗

(𝑤 𝑖 𝑗 × 𝑥 𝑗 )](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-21-320.jpg)

![行列とベクトルの乗算

全結合層

x[N] y[M]

w[N][M]

x =

w[N][M] x[N] y[M]

メモリバンド幅で性能が決まる

Xeon E5-2690v3 Tesla K40

68 GB/s 288 GB/s

ピークメモリバンド幅

行列 ベクトル](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-22-320.jpg)

![全結合層

x[N] y[M]

w[N][M]

x =

w[N][M] x[N] y[M]

ミニバッチ: 複数データで同時学習

行列 ベクトル](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-23-320.jpg)

![行列と行列の乗算

全結合層

x[K][N] y[K][M]

w[N][M]

x =

w[N][M] x[K][N] y[K][M]

高い演算能力を発揮できる

Xeon E5-2690v3 Tesla K40

0.88 TFLOPS 4.29 TFLOPS

ピーク演算性能(単精度)

行列 行列](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-24-320.jpg)

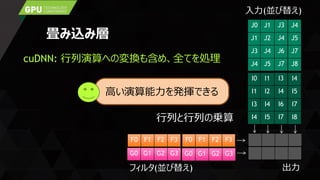

![CNN: Convolution Neural Network

フルコネクション (全結合層) cuBLAS

コンボリューション (畳み込み層) cuDNN

LeNet5 [LeCun et al.,1998]](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-26-320.jpg)

![LENET5

LeNet5 [LeCun et al.,1998]

OutputsFilter

(Expanded)

Inputs

16

100 * batch size

150

150](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-38-320.jpg)

![GOOGLENET

GoogLeNet [Szegedy et al.,2014]

OutputsFilter

(Expanded)

Inputs

192

3136 * batch size

576

576

LENET5 GOOGLENET

0.24 x Bs 346 x Bs

1回の演算量(MFLOP)](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-39-320.jpg)

![cuDNN API

畳み込み演算

cudnnConvolutionForward()

cudnnConvolutionBackward[Bias|Filter|Data]()

活性化

cudnnActivationForward()

cudnnActivationBackward()

プーリング

cudnnPoolingForward()

cudnnPoolingBackward()

ソフトマックス

cudnnSoftmaxForward()

cudnnSoftmaxBackward()

…](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-40-320.jpg)

![GPUはディープラーニングの全フェーズを加速

cuBLAS

LeNet5 [LeCun et al.,1998]](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-41-320.jpg)

![性能測定結果

AlexNet [A. Krizhevsky et al.,2012]

2.5M

18M

23M

43M

0

10

20

30

40

50

16 Core CPU GTX Titan Titan Black

cuDNN v1

Titan X

cuDNN v2

画像数(M)

1日あたりの学習画像数 (Caffe)

E5-2698 v3 @ 2.3GHz / 3.6GHz Turbo](https://image.slidesharecdn.com/05-akira-150819140404-lva1-app6892/85/GPU-42-320.jpg)