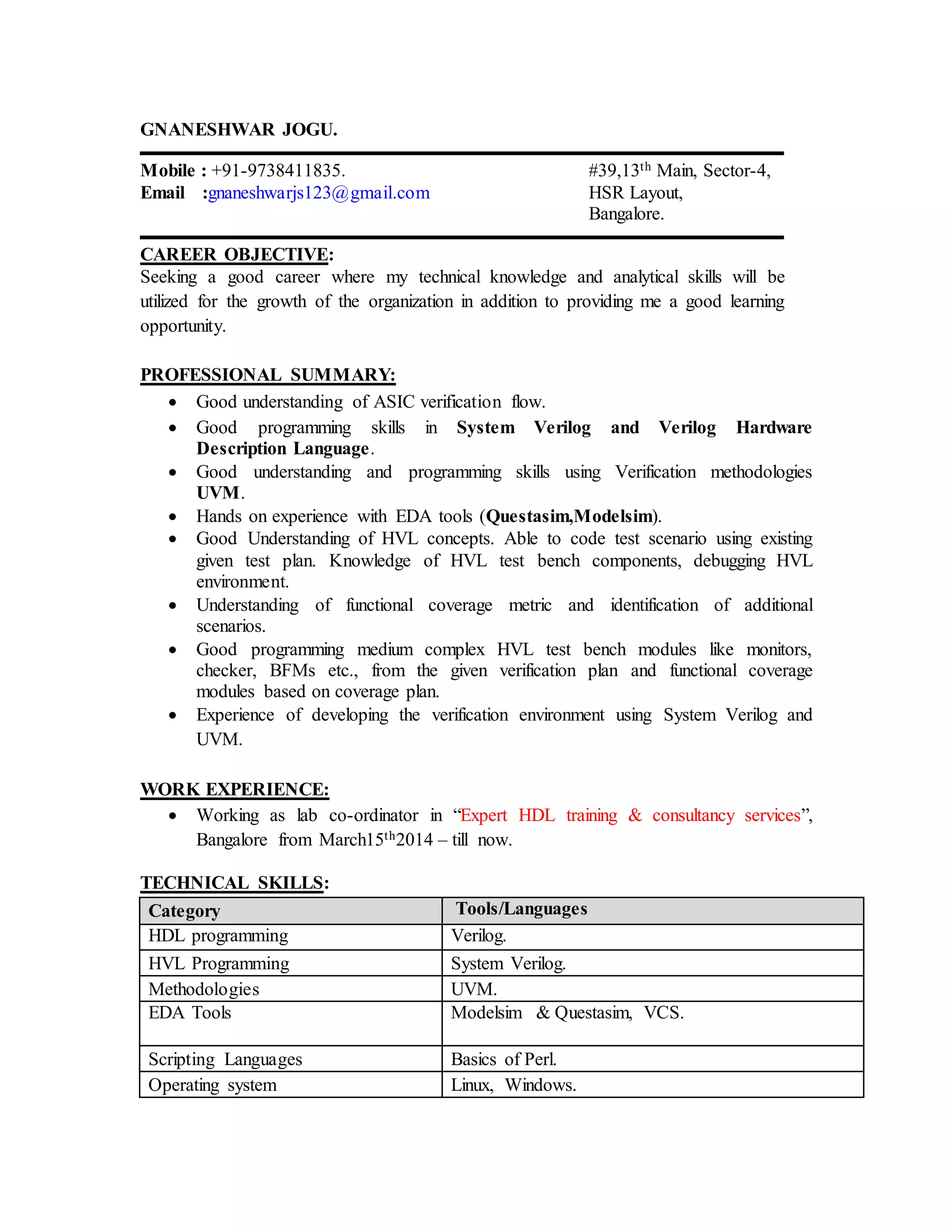

Gnaneshwar Jogu is seeking a career where he can utilize his technical knowledge and analytical skills. He has good understanding of ASIC verification flow and skills in System Verilog and Verilog. He has hands-on experience with tools like Questasim and Modelsim. He has worked on verification projects including UART, FIFO, AMBA APB3.0 interface, and dual port RAM. He is looking to leverage his qualifications and project experience for the growth of an organization.