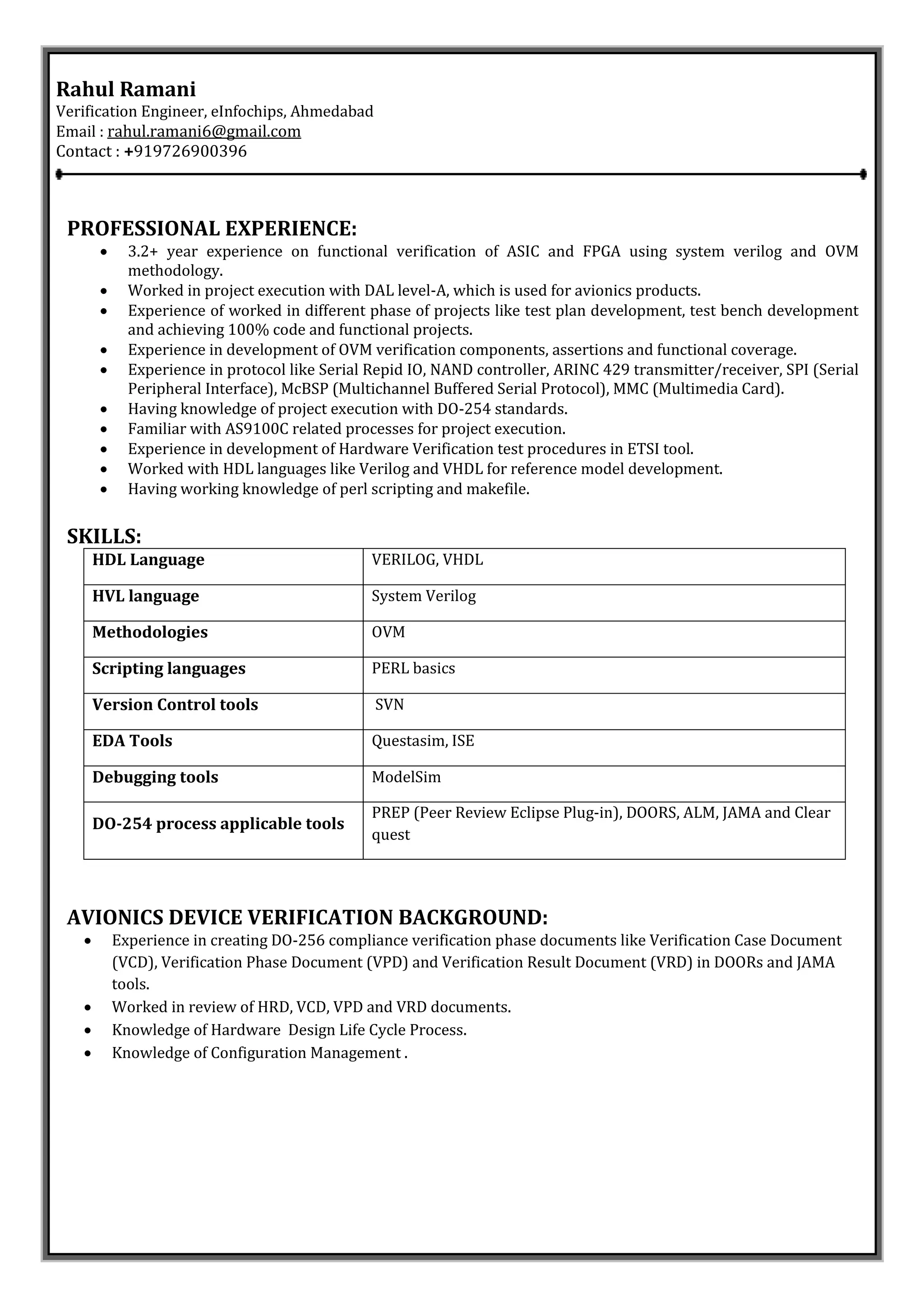

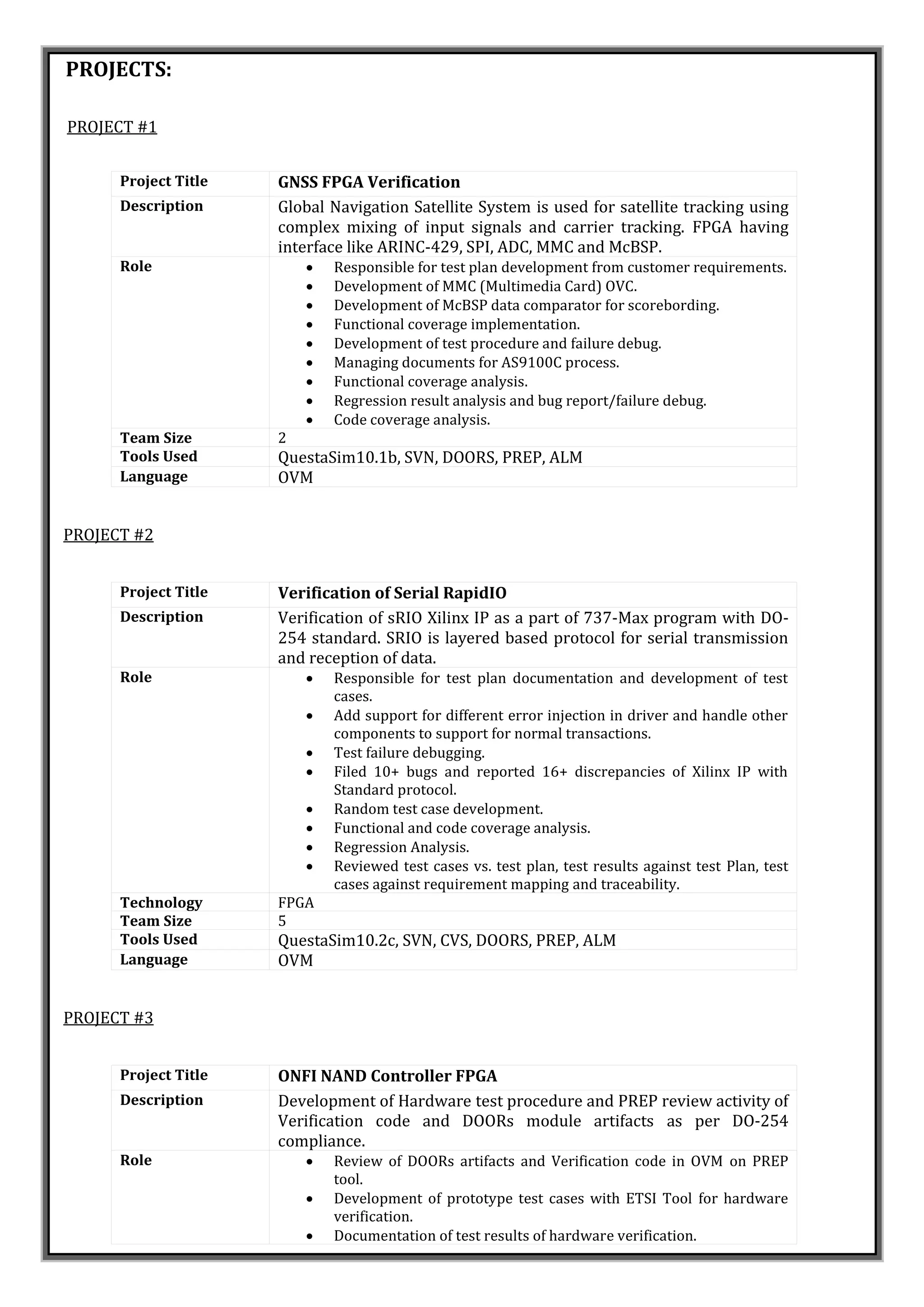

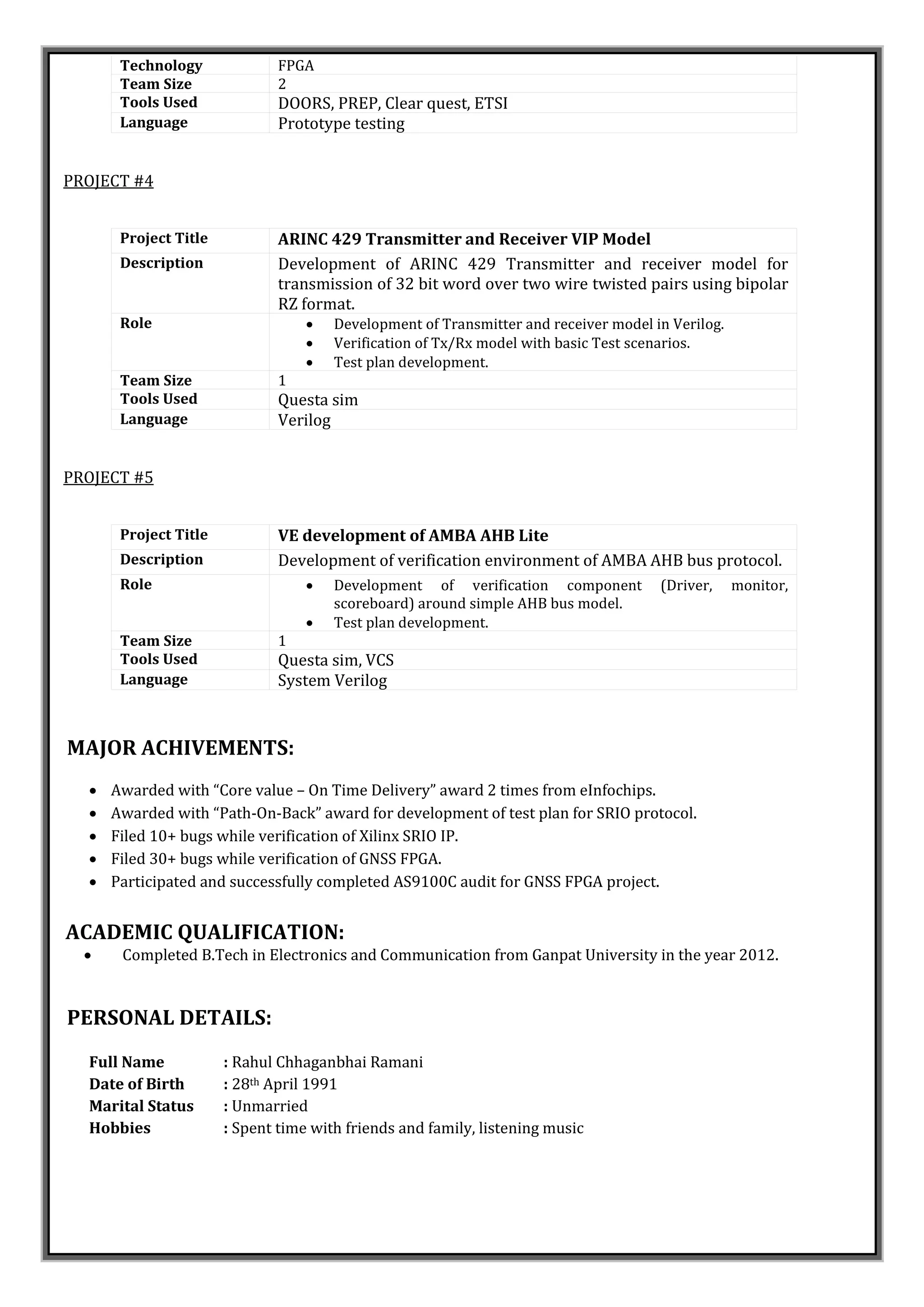

Rahul Ramani has over 3 years of experience in functional verification of ASICs and FPGAs using SystemVerilog and OVM methodologies. He has worked on projects involving DAL level-A components for avionics and has experience developing testbenches, achieving code and functional coverage, and verifying protocols like Serial RapidIO. Rahul is skilled in Verilog, VHDL, SystemVerilog, OVM, and scripting languages like Perl. He has experience with verification tools like QuestaSim and debugging tools like Modelsim. Rahul has also worked on verification projects involving DO-254 standards where he created compliance documents and reviewed verification artifacts.