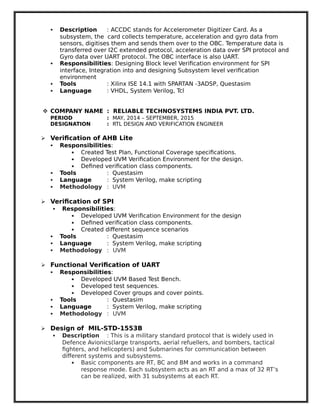

Vanshlata is a project associate with over 3 years of experience in VLSI design and verification. She has expertise in digital design, verification methodologies like UVM, and tools like Questasim and Xilinx. She has worked on projects involving ASIC/FPGA design, SOC verification, and protocol verification. Her experience includes developing verification environments, testbenches, test cases, and functional coverage for designs like radar seekers and accelerometer systems. She has a post-graduate diploma in ASIC design and verification and has cleared the GATE exam multiple times.