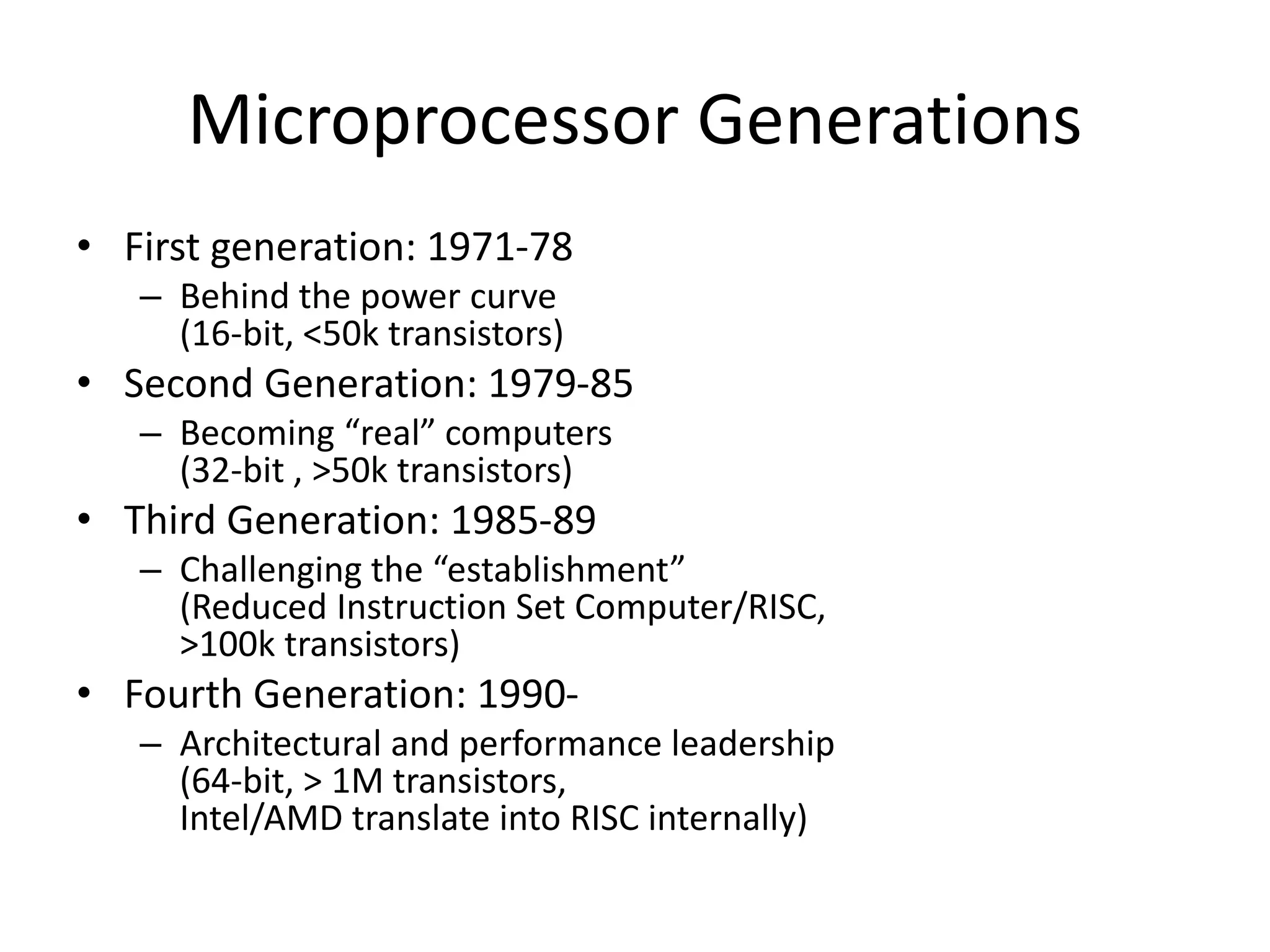

The document traces the evolution of microprocessors from the early 4-bit Intel 4004 in 1971 to the 64-bit MIPS R4000 in 1991. It describes the key innovations of each generation including increased bit width, transistor count, and performance. The first generation from 1971-1978 had processors with less than 50k transistors and under 50k instructions per second. The second generation from 1979-1985 saw the introduction of 32-bit processors with over 50k transistors. The third generation from 1985-1989 included reduced instruction set computers with over 100k transistors. The fourth generation from 1990 onward introduced 64-bit architectures with over 1 million transistors and performance leadership.