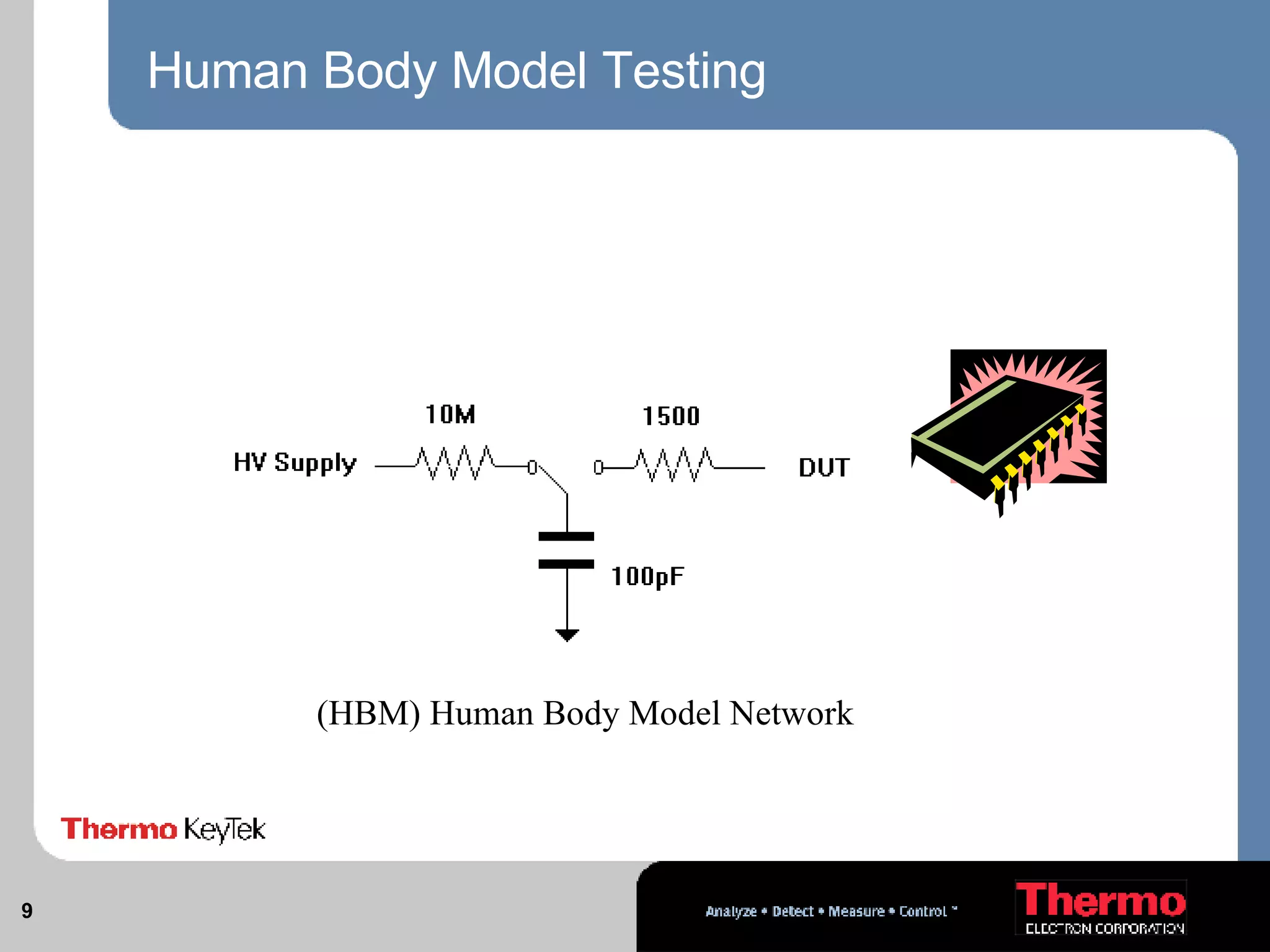

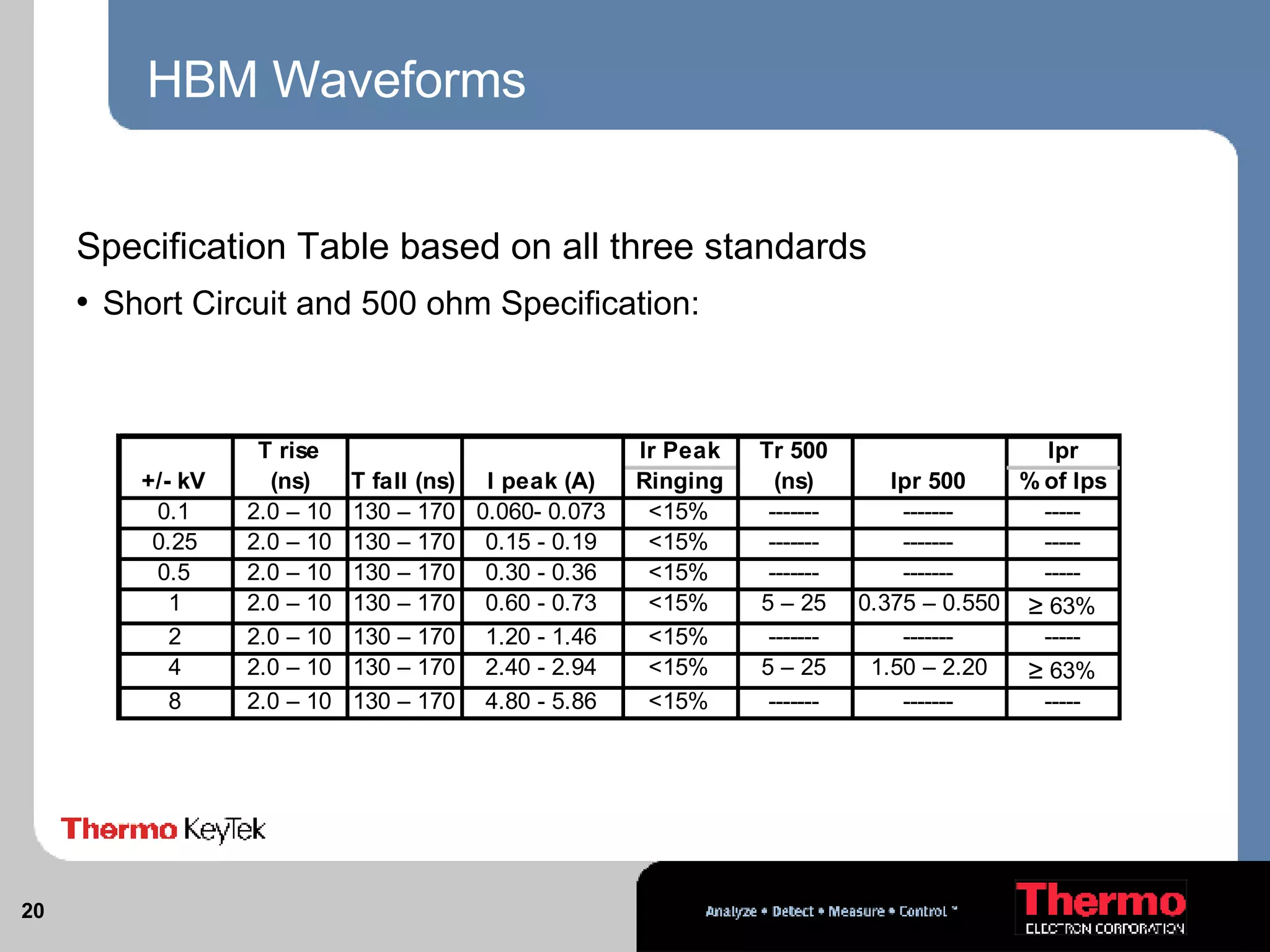

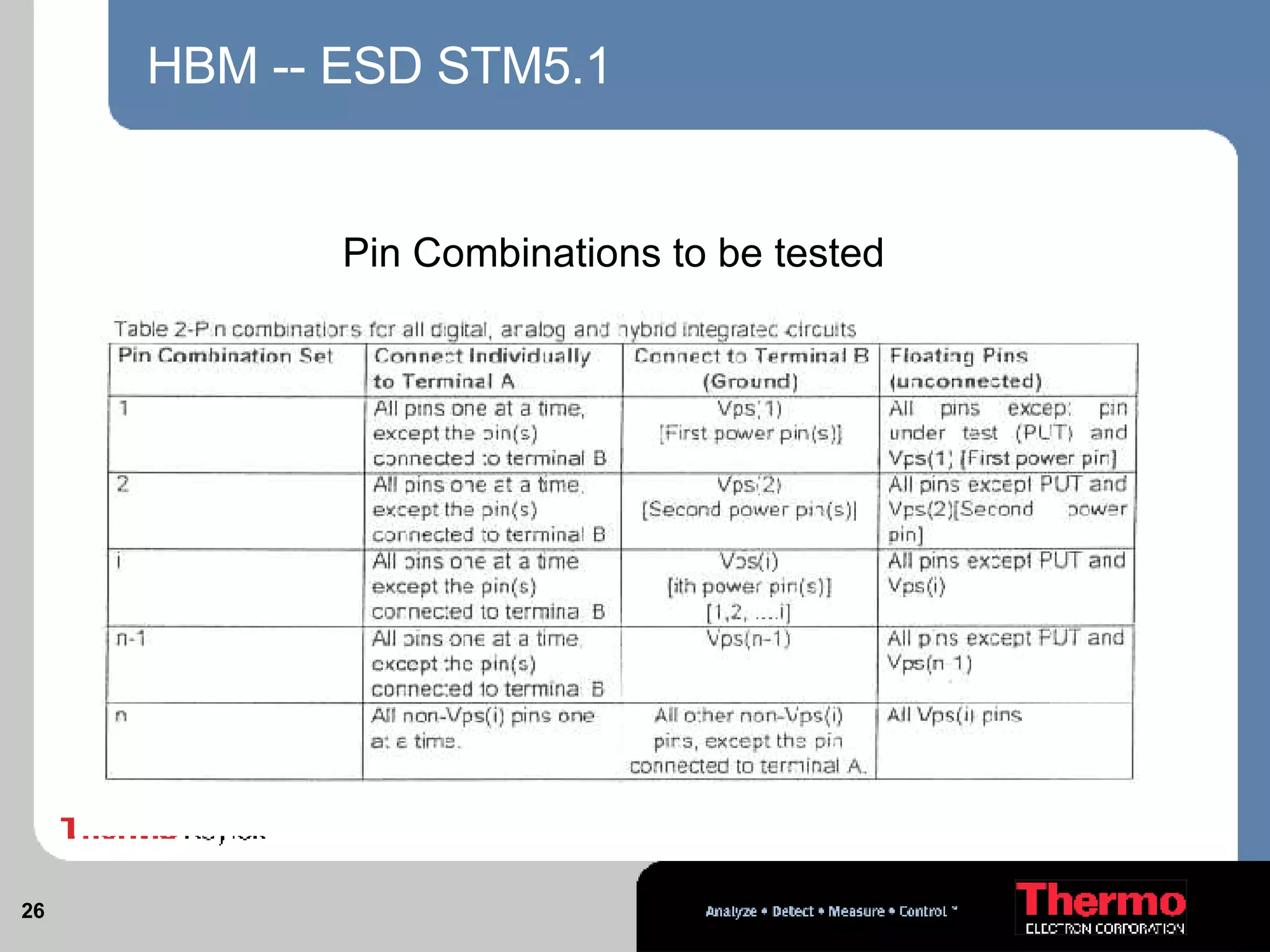

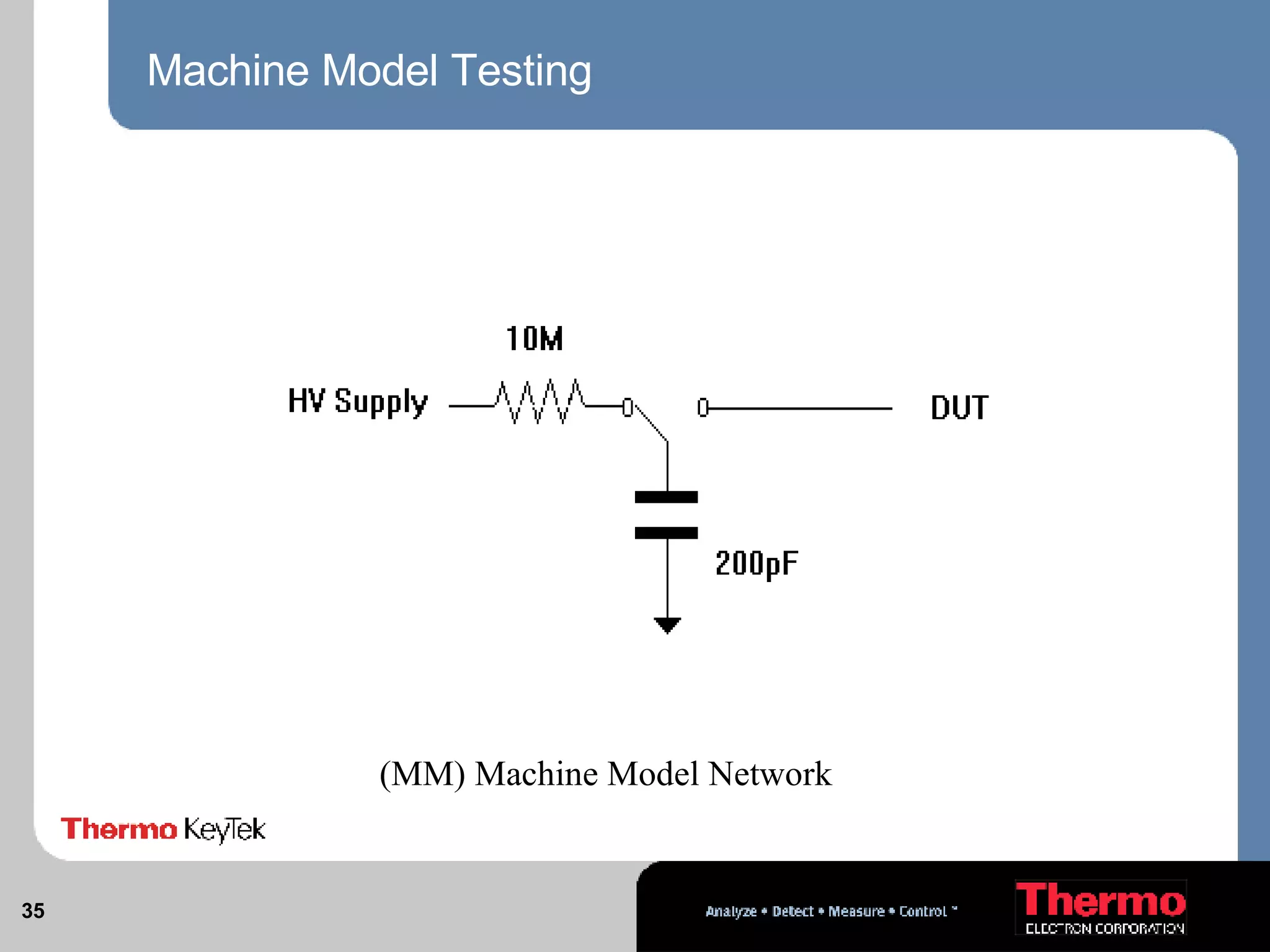

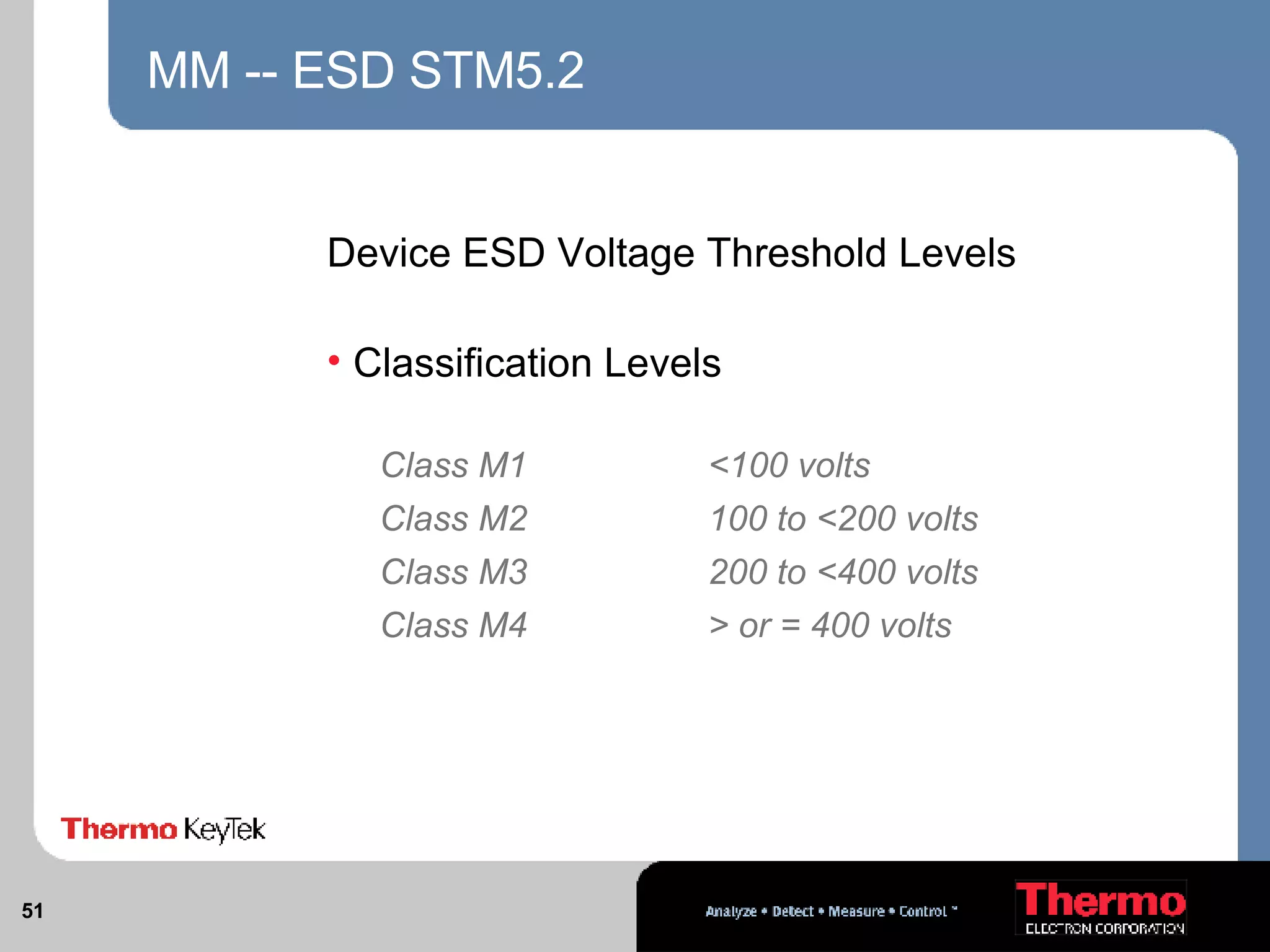

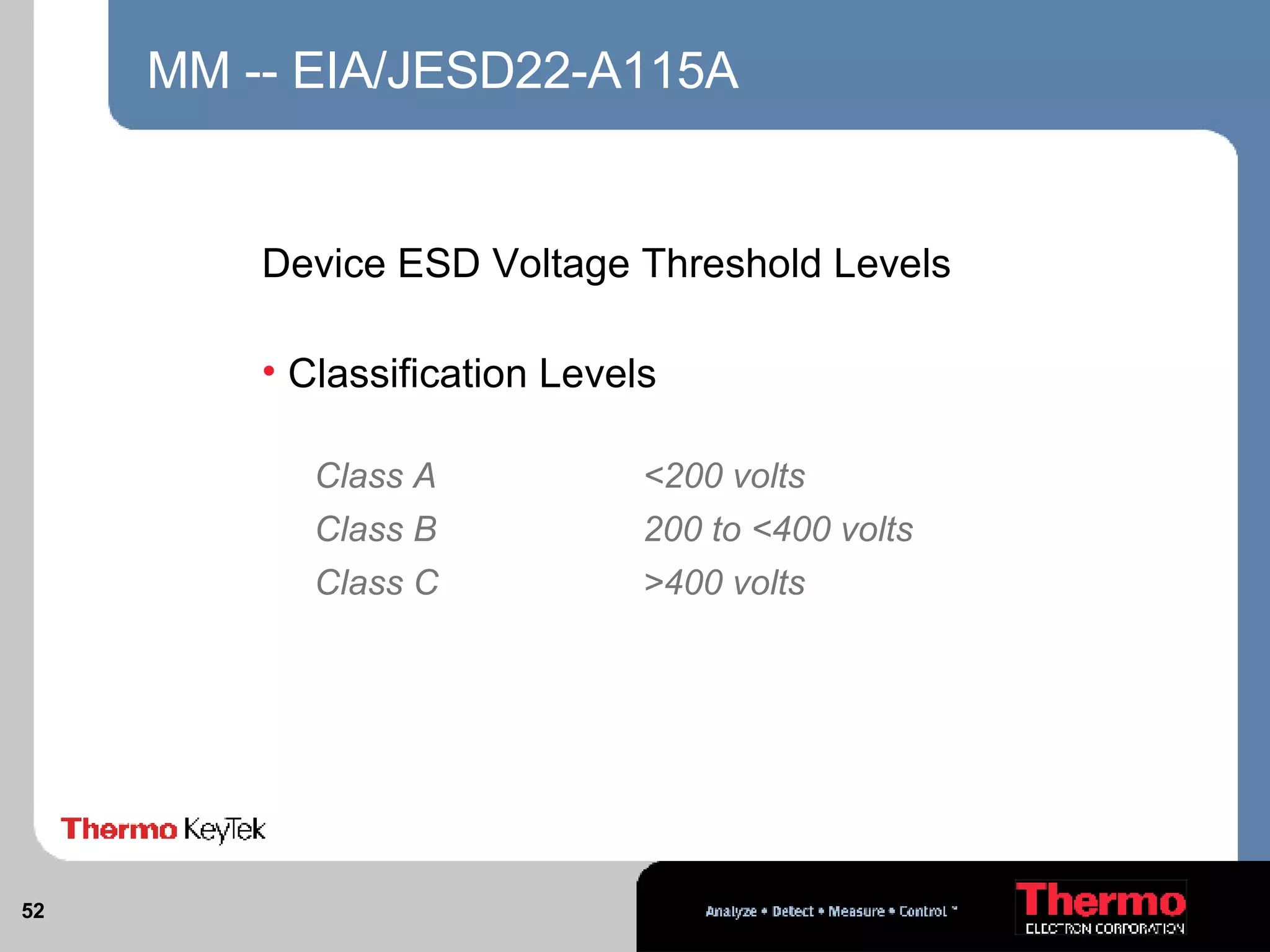

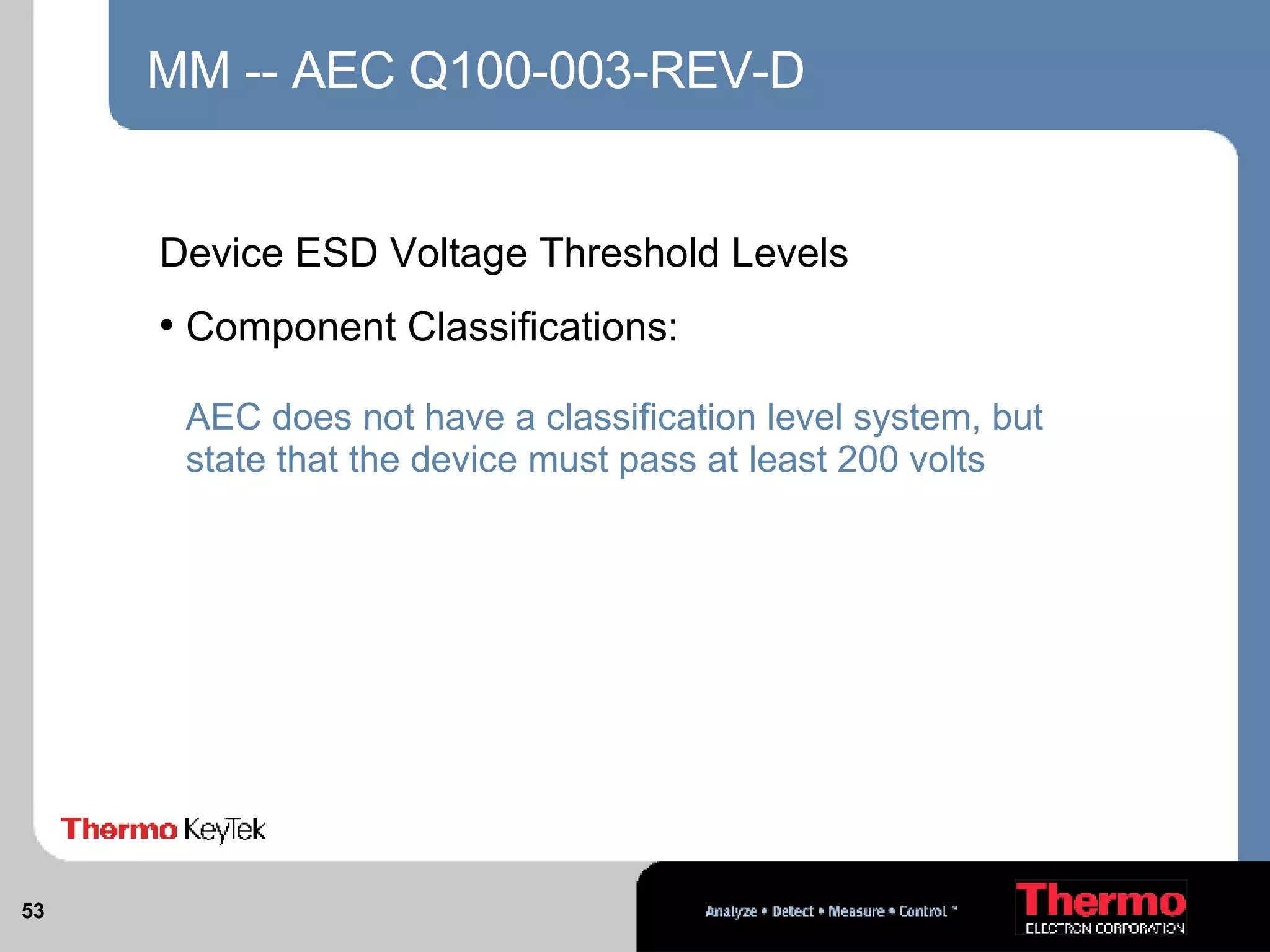

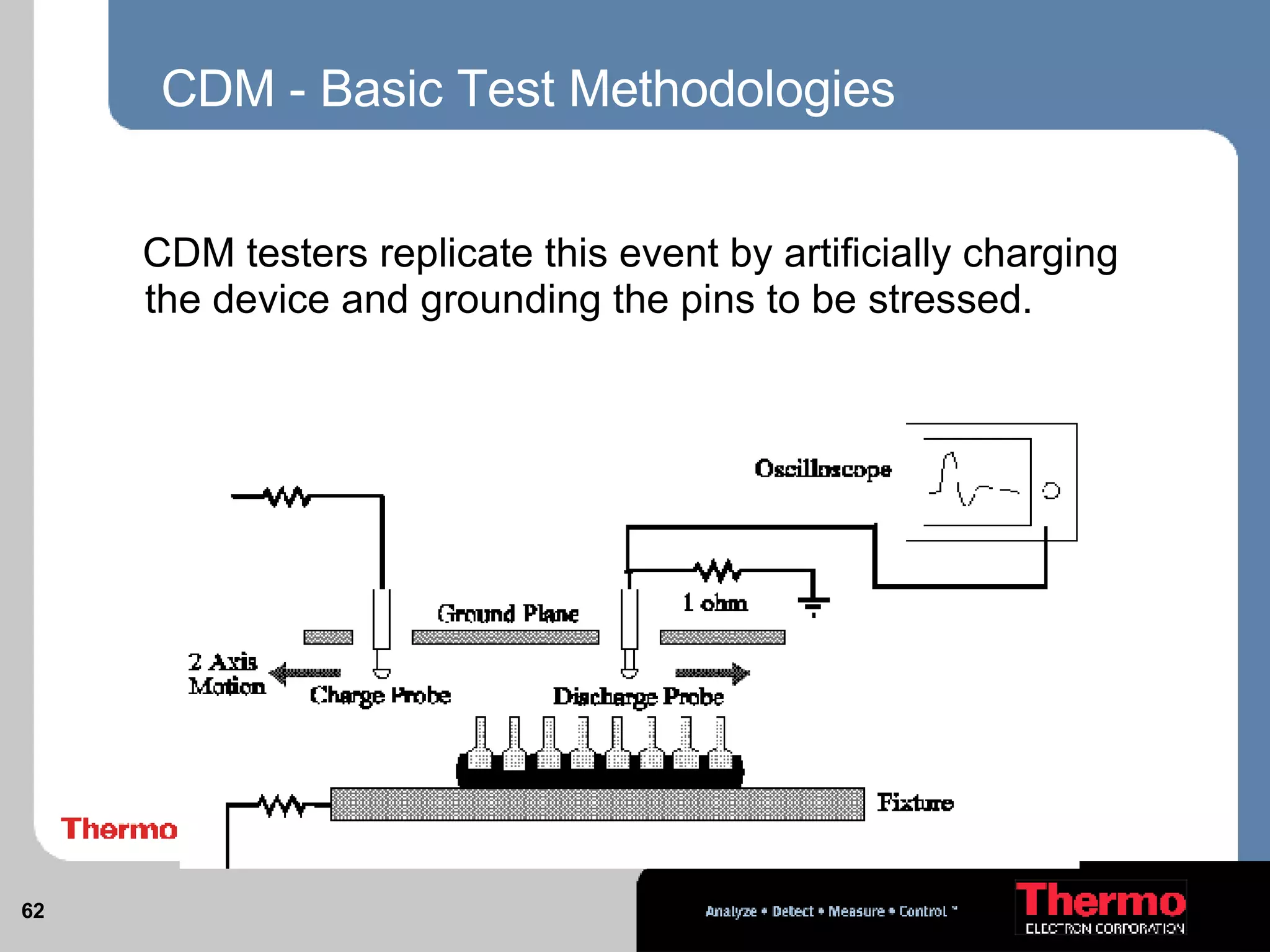

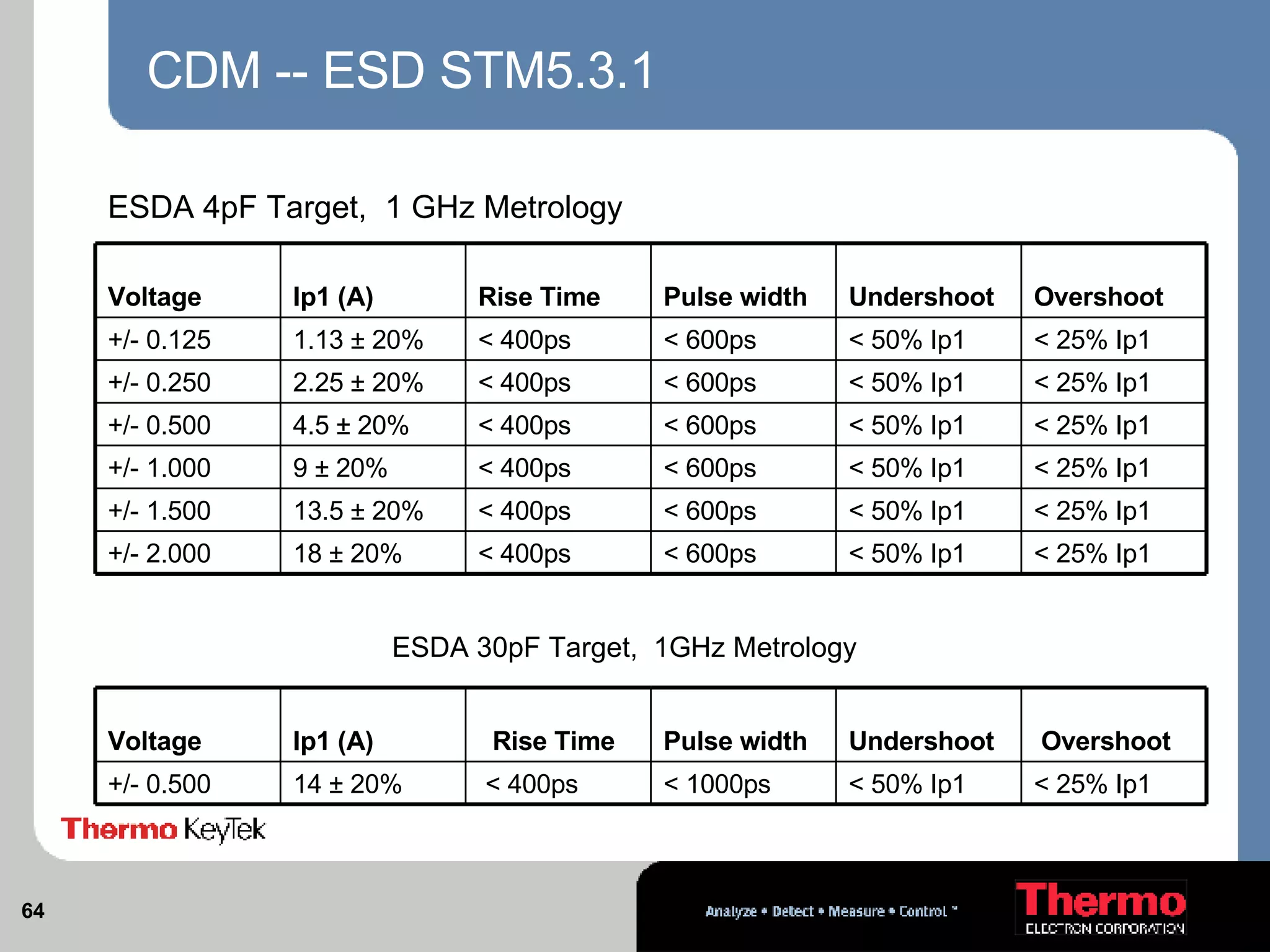

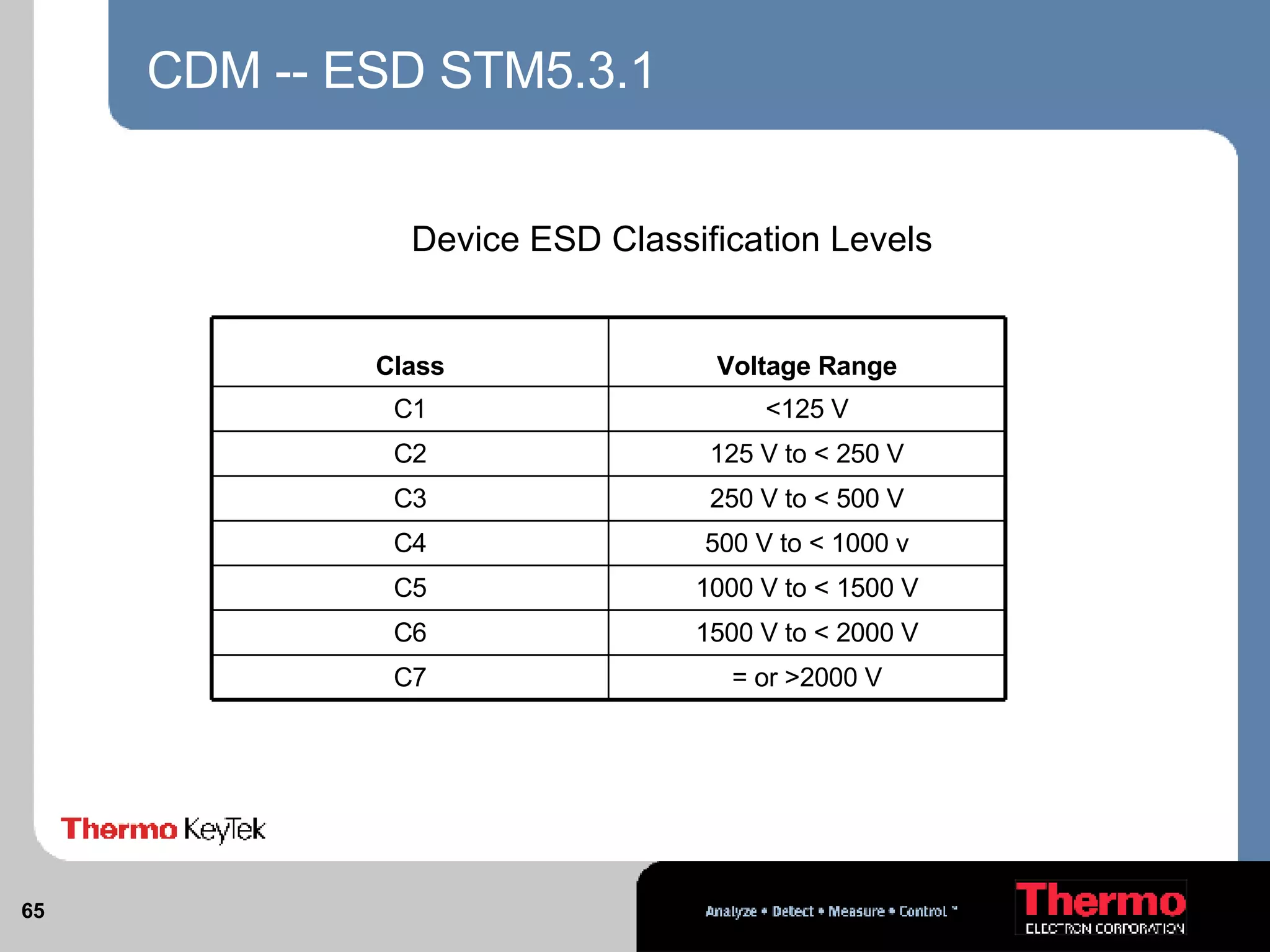

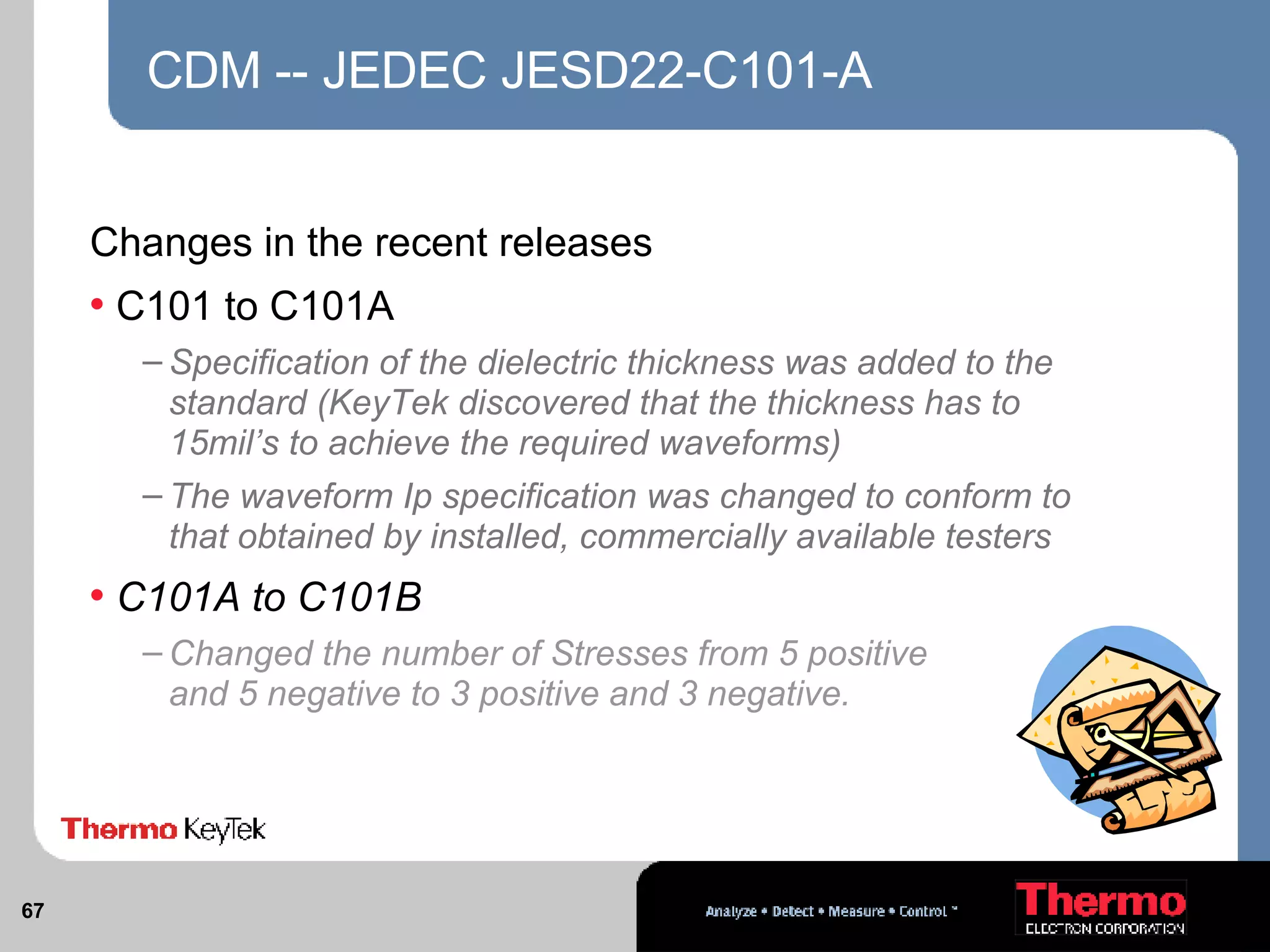

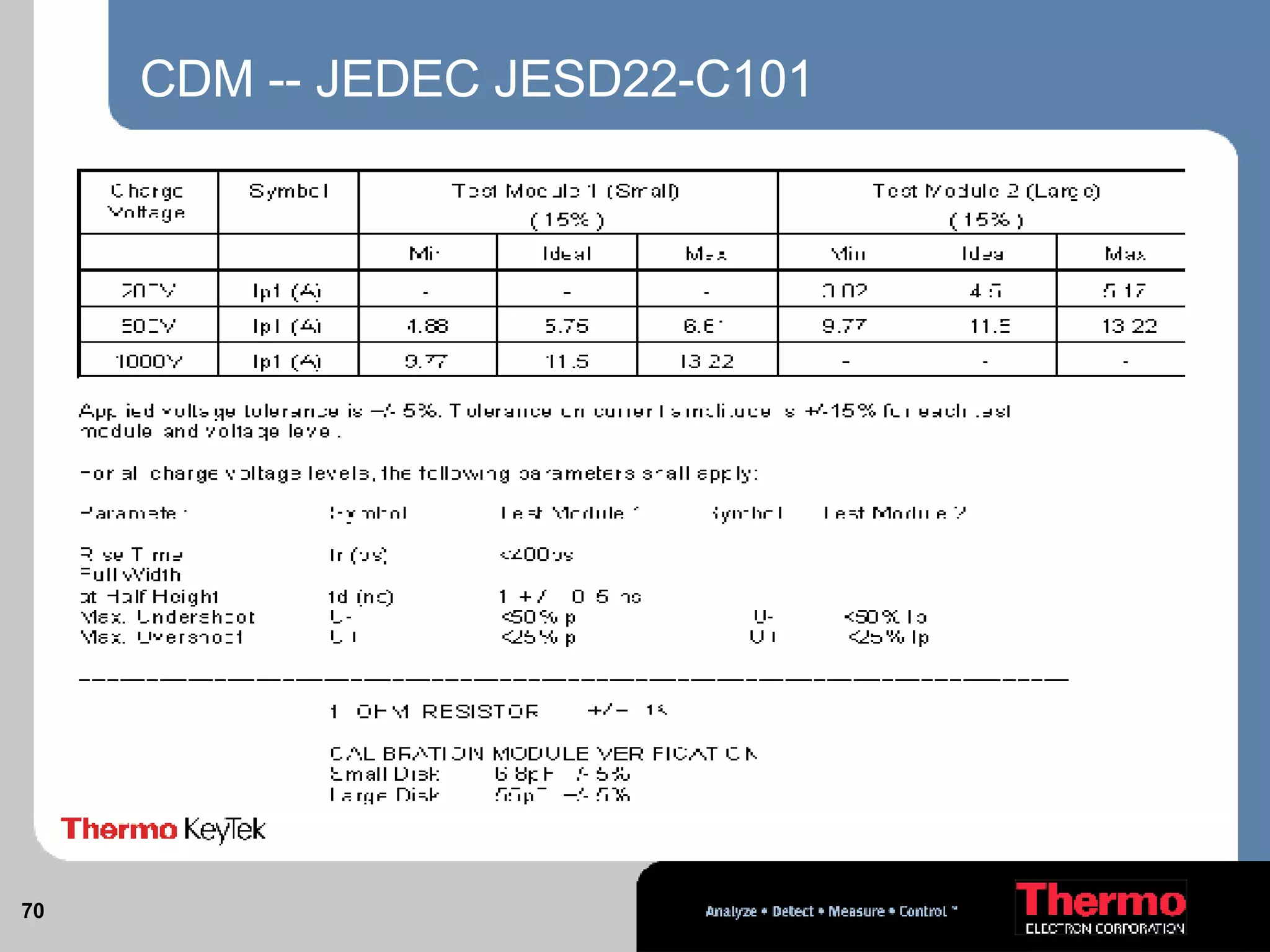

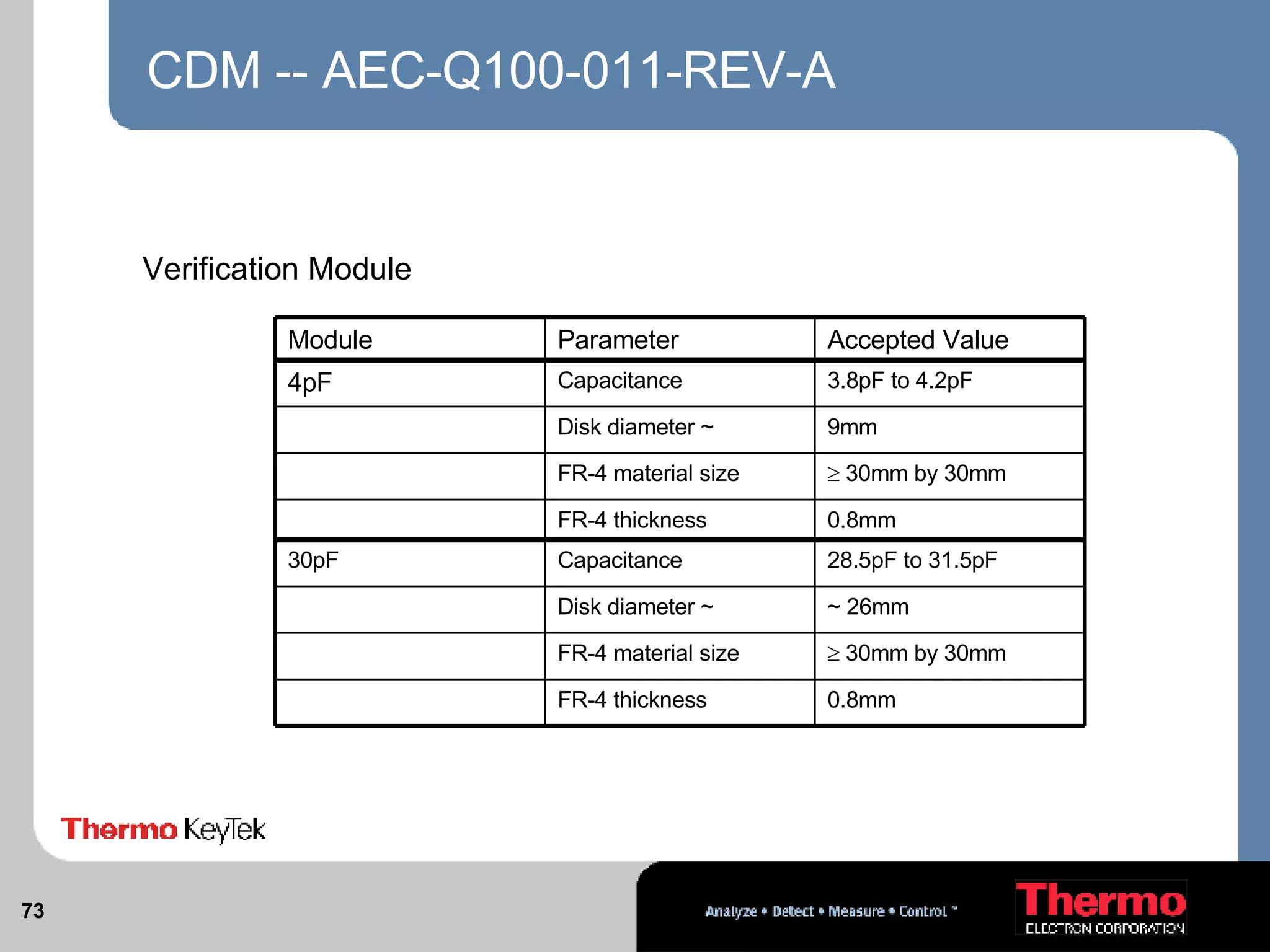

The document discusses different types of ESD (electrostatic discharge) and EOS (electrical overstress) testing methods. It provides an overview of the Human Body Model (HBM), Machine Model (MM), and Charged Device Model (CDM) test methods, including their relevant standards, test procedures, waveforms, and device classification levels. It also discusses the history and evolution of these ESD test methods over time as standards have been developed and refined by organizations like ESDA, JEDEC, AEC, and others.