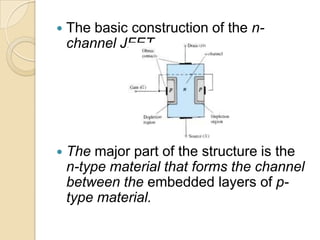

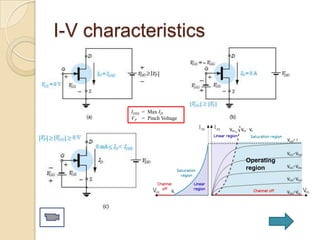

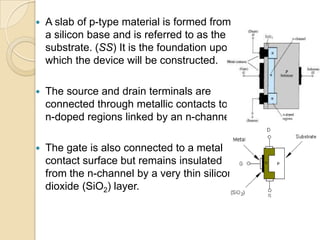

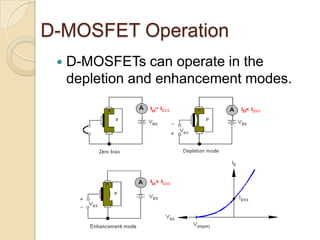

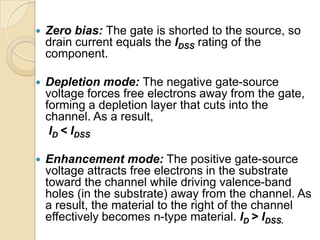

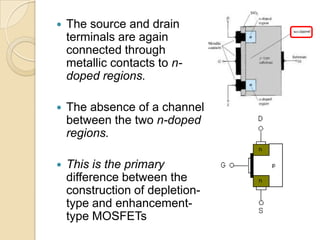

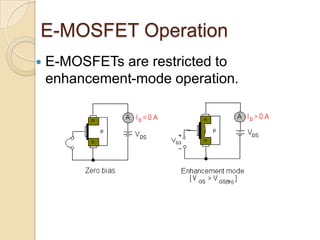

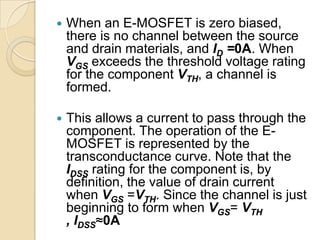

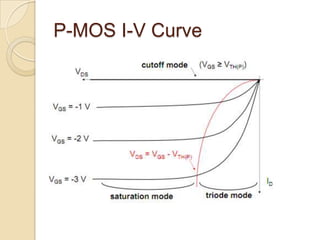

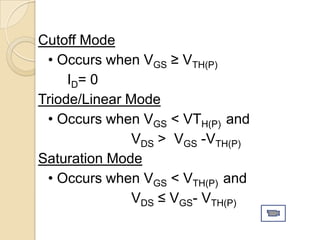

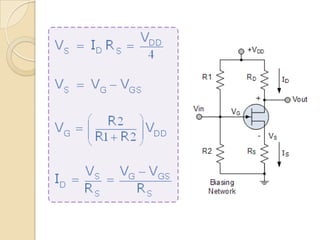

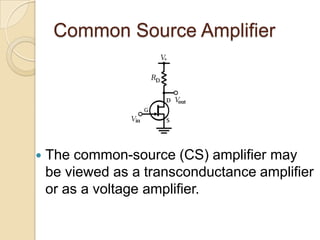

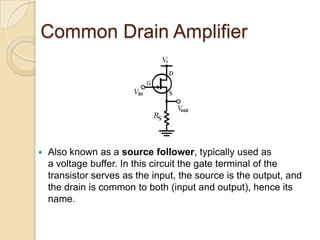

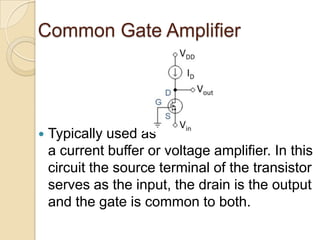

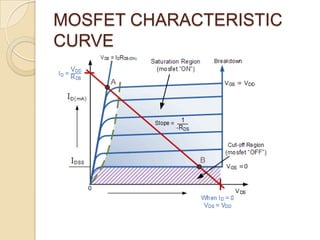

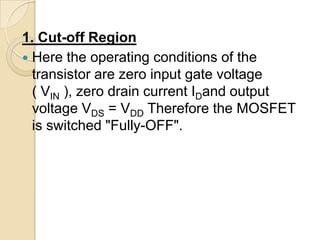

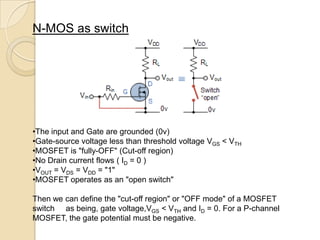

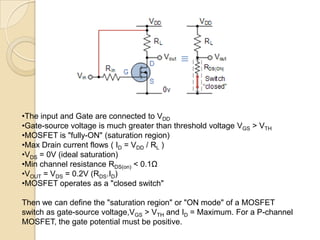

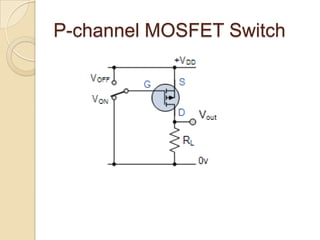

The document discusses field effect transistors (FETs), specifically junction field effect transistors (JFETs) and metal-oxide-semiconductor field effect transistors (MOSFETs). It describes the basic construction, operation, and characteristics of n-channel and p-channel JFETs and MOSFETs. Application circuits for JFET and MOSFET amplifiers and switches are also presented. Key differences between BJTs, JFETs, and MOSFETs are highlighted.