The document outlines the design of an efficient 16-bit full adder circuit capable of adding three 16-bit numbers using two strategies: a wait strategy and a design for all cases (DAC) strategy. It details the architecture of the circuit, including the division of the addition process into smaller units using full adders, propagation delays for different configurations, and the trade-offs between speed and cost in the two strategies. The results demonstrate that while the DAC strategy reduces propagation delay compared to the wait strategy, it also incurs higher costs.

![Digital System Design

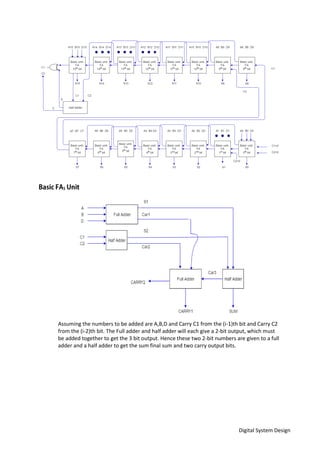

The basic unit of FA5 is designed using 2 Full adders and 2 Half adders.

The green line shows the critical path of the schematic circuit.

The timing simulation is performed for the above design and the waveforms are recorded.

The screenshot of the worst case delay(critical path) is shown below. This is also known as

propagation delay. There exists minor variation in worst case delay in the outputs of S[16]

and S[17] in the order of 1/10th

. So its neglected.](https://image.slidesharecdn.com/ece451project1reportvisheshshravan-161019085144/85/Ece-465-project_1_report_vishesh_shravan-6-320.jpg)

![Digital System Design

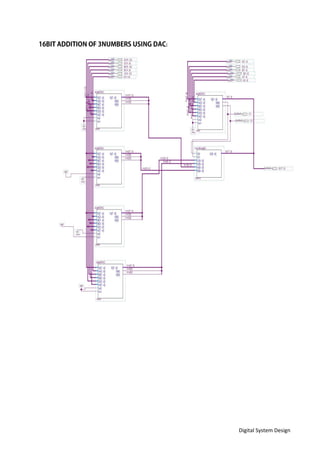

Each 4-bit adder is fed with three 4-bit input buses and 3 carry-ins. As we know from the 3 number

addition, there can be two carries per column. The output of each 4-bit adder block is a 4-bit sum

output fed into a bus S[3..0] and 2 carry outs C1 and C2.

We know, in the wait strategy, the carry out C1 from ith

adder is fed to the (i+1)th

bit adder and the

C2 from ith

adder is fed to the (i+2)th

adder. In our 4-bit adder, likewise the C2 from the third adder

should be fed to the fifth bit and the C1 from the 4th

adder should also be fed to the fifth bit. To have

two output from the 4 bit wait block, we add these two bits using a half adder. The Sum of this half

adder acts as C1 input for the fifth bit and the Carry out of this half adder is given as an input to the

XOR gate along with the C2 of the 4th

bit to generate the Carry(C2) for the sixth bit.

The 4-bit adder(LSB) is fed with 3 4-bit, input buses. The carry ins In1, In2 and In3 are zero. The MSB

part contains 4 similar adders. Each have 3 4-bit input buses. The In2 pin of each MSB block is

grounded as there is no C2 for the first bit of the MSB. The values in1 and In3 for each MSB block is

different and is either 00,01,10 or 11. There is a 4:1 mux to select 1 out of the 4 MSB blocks. The

mux is fed with the carry outs from the LSB. On the basis of theses carry outs one MSB block is

selected. From this 8 bit block, we get an 8 bit sum fed into a bus S[7..0] and two carry outs C1 and

c2.

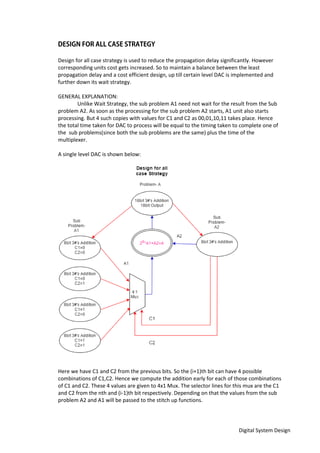

As we can see from the diagram we have 1 8-bit LSB and 4 8-bit MSB blocks.

The 8-bit block is fed with input buses A, B and D and two carry ins In1 and In2. Each 8-bit block gives

8 bit SUM S[7..0] and two carry outs.

The LSB 8-bit block has its carry in pins grounded as there is no carry ins to the first and the second

bit. There are four 8 bit blocks. The design is similar to the 8-bit block design which consisted of 4-bit

LSB and four 4-bit MSB. The multiplexer is fed with the carry outs form the LSB. On the basis of these

Carry outs one out of the four MSBs are selected. The output from this level would be the 16-bit sum

and 2 carry out bits. As this is the last level, the carry outs would be fed into the output bus along

with the 16-bit Sum, thus giving an 18-bit sum for the three 16-bit inputs.

Number of inputs in 1-4Bit WS= 20+2+2=24inputs

Number of inputs in 1-4x1 Mux= 6inputs

Total area of 16Bit Circuit= 25*24 + 6*6=636inputs

(i) For 16Bit 3numbers addition:

Delay of 4Bit W.S = 4*10p+1HA+1XOR=44p

Delay of 4x1 Mux=6p

Total delay of the 16bit circuit =44+ 2(4x1 MUX)= 44+12=56p](https://image.slidesharecdn.com/ece451project1reportvisheshshravan-161019085144/85/Ece-465-project_1_report_vishesh_shravan-12-320.jpg)

![Digital System Design

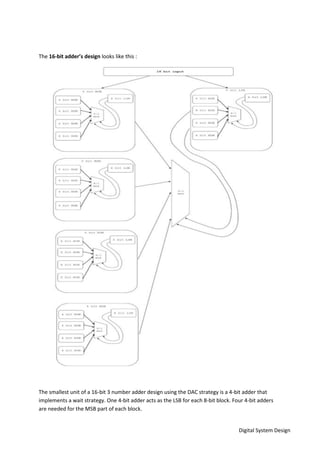

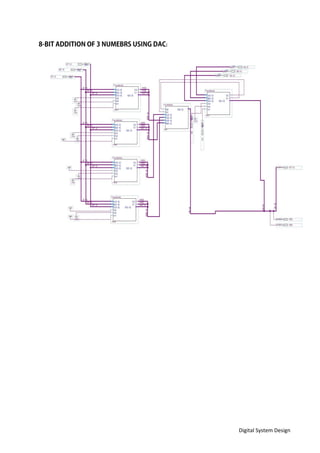

The 4bit wait strategy addition of 3 numbers is shown below. This is a simple wait strategy

addition wherein the C1 and C2 of the ith

bit addition block is given to (i+1)th

and (i+2)th

FA5.

The C1 and C2 for the last 2bit addition differ depending upon the previous sub problem. For

the inputs from [0..3] the C1 C2 and C2 of the 0th

and 1st

bit FA5 unit will be zero.

Now this is blocked up into a single unit with arrays of inputs being A[3..0],B[3..0],D[3..0] and

output S[3..0] with C1 and C2. The next level is the DAC implementation.

We know, in the wait strategy, the carry out C1 from each single bit adder is fed to the (i+1)th

adder

and the C2 from each single bit adder is fed to (i+2)th

adder. In our 4-bit adder, the C2 from the third

adder should be fed to the fifth bit and the C1 from the 4th

adder should also be fed to the fifth bit.

To minimize the inputs for the block level implementation of the 4-bit adder we add these two bits

using a half adder. The Sum of this half adder acts as C1 input for the fifth bit and the Carry out of

this half adder is XOR’ed with the C2 of the 4th

bit to get the Carry for the sixth bit.](https://image.slidesharecdn.com/ece451project1reportvisheshshravan-161019085144/85/Ece-465-project_1_report_vishesh_shravan-15-320.jpg)

![Digital System Design

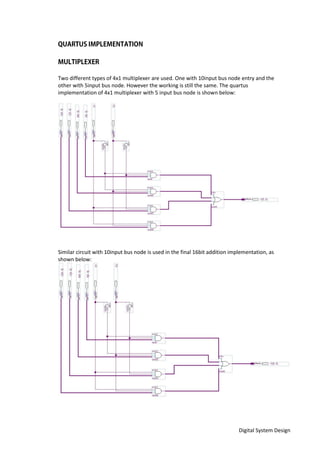

It can be seen that the above designed circuits produce proper results for every type of input

numbers. From the waveform graph it is clear that the Ts and T are not the same.

TYPE T(As defined..)[ns] AT2

Ts[ns]

1.WAIT STRATEGY 13.767 15920.94 units 25.568

2.DAC STRATEGY 15.794 158650.65 units 18.623

From the above table we can conclude that the propagation delay for the DAC strategy is

less than that of the Wait strategy, but it comes with a higher cost.](https://image.slidesharecdn.com/ece451project1reportvisheshshravan-161019085144/85/Ece-465-project_1_report_vishesh_shravan-20-320.jpg)