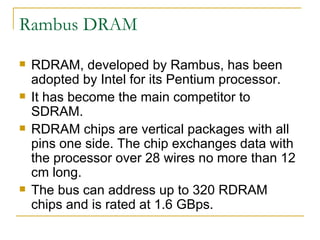

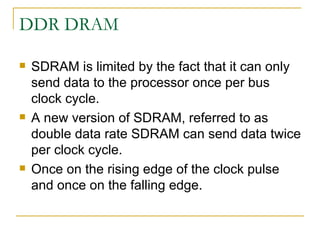

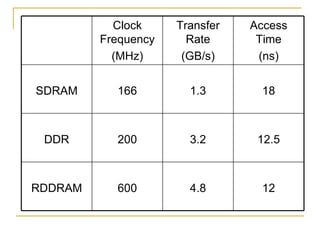

Asynchronous DRAM (ADRAM) is widely used due to its internal architecture and interface to the processor's memory bus. However, ADRAM has slow access times which degrade system performance. Synchronous DRAM (SDRAM) was developed to exchange data with the processor synchronized by an external clock, allowing full processor speed without wait states. Later, Double Data Rate SDRAM and Rambus DRAM were introduced to increase data transfer rates.