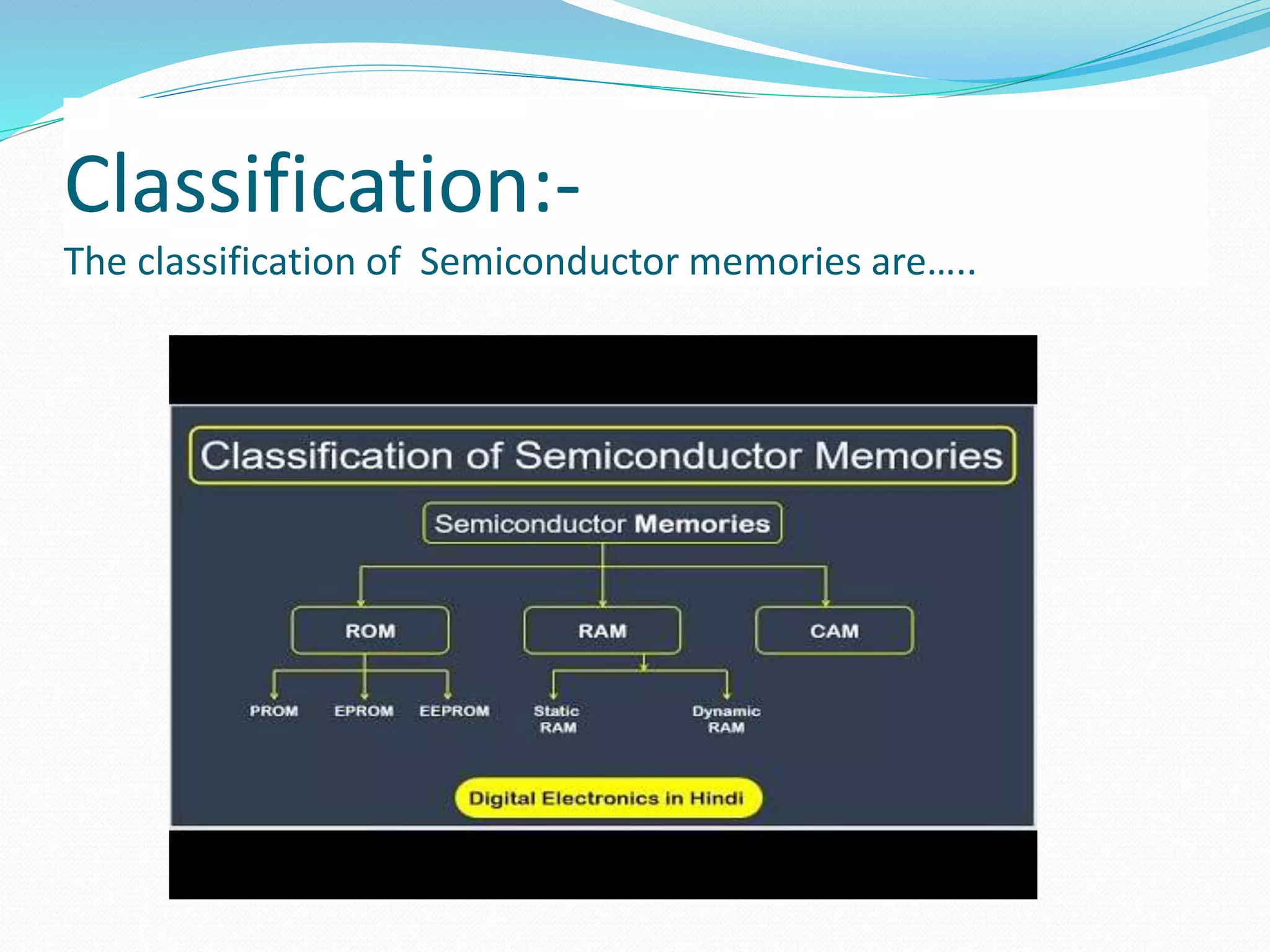

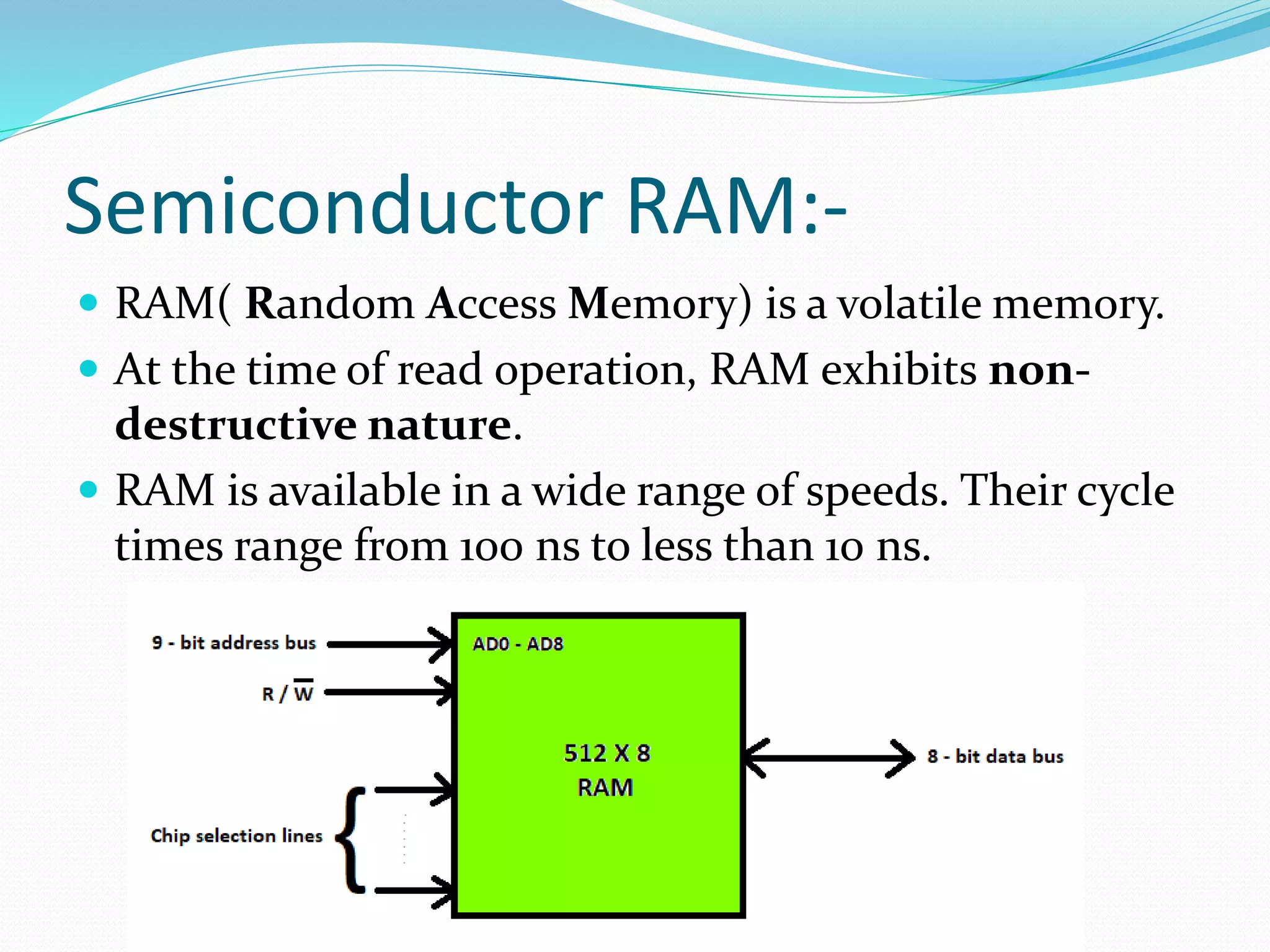

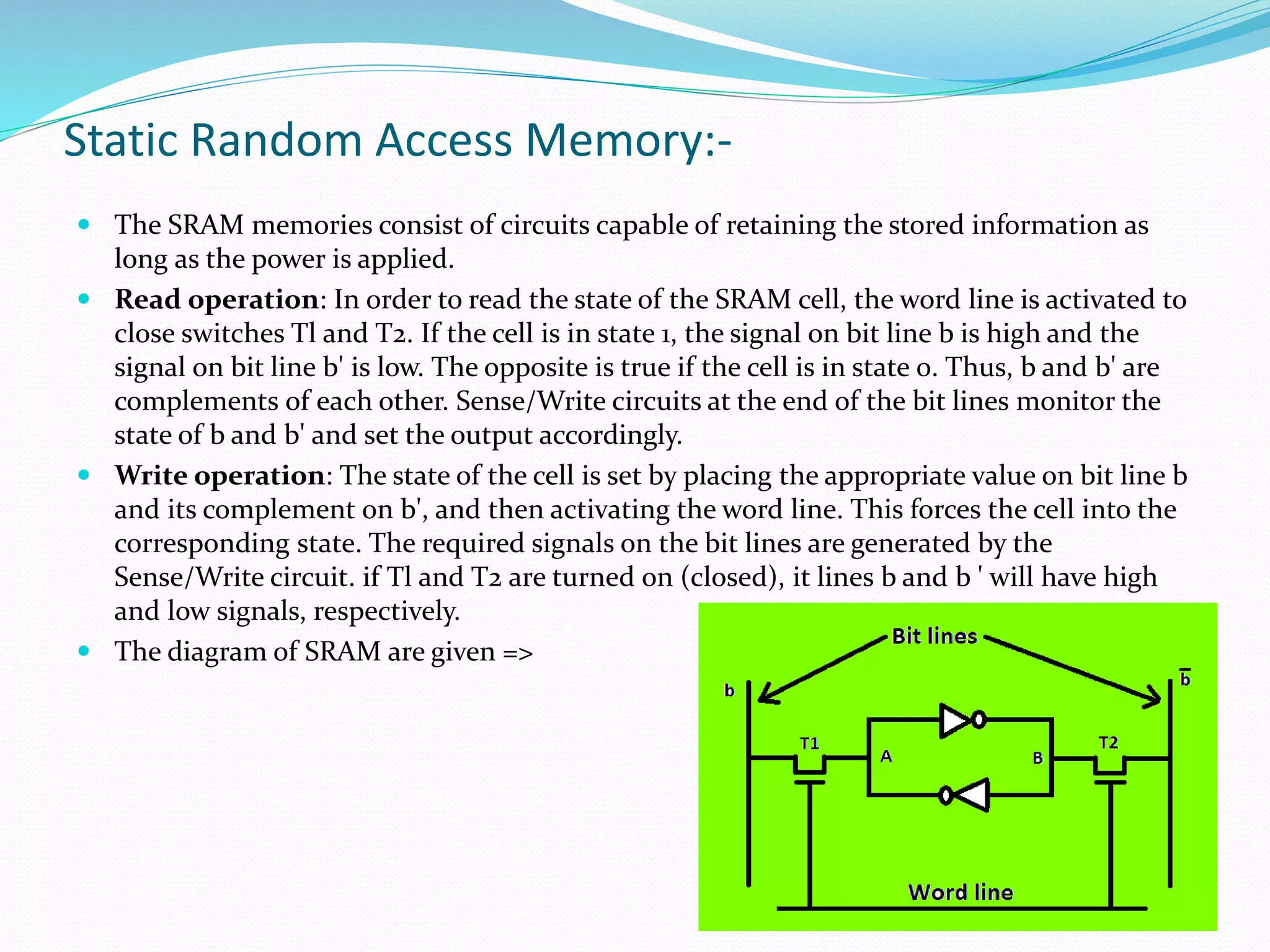

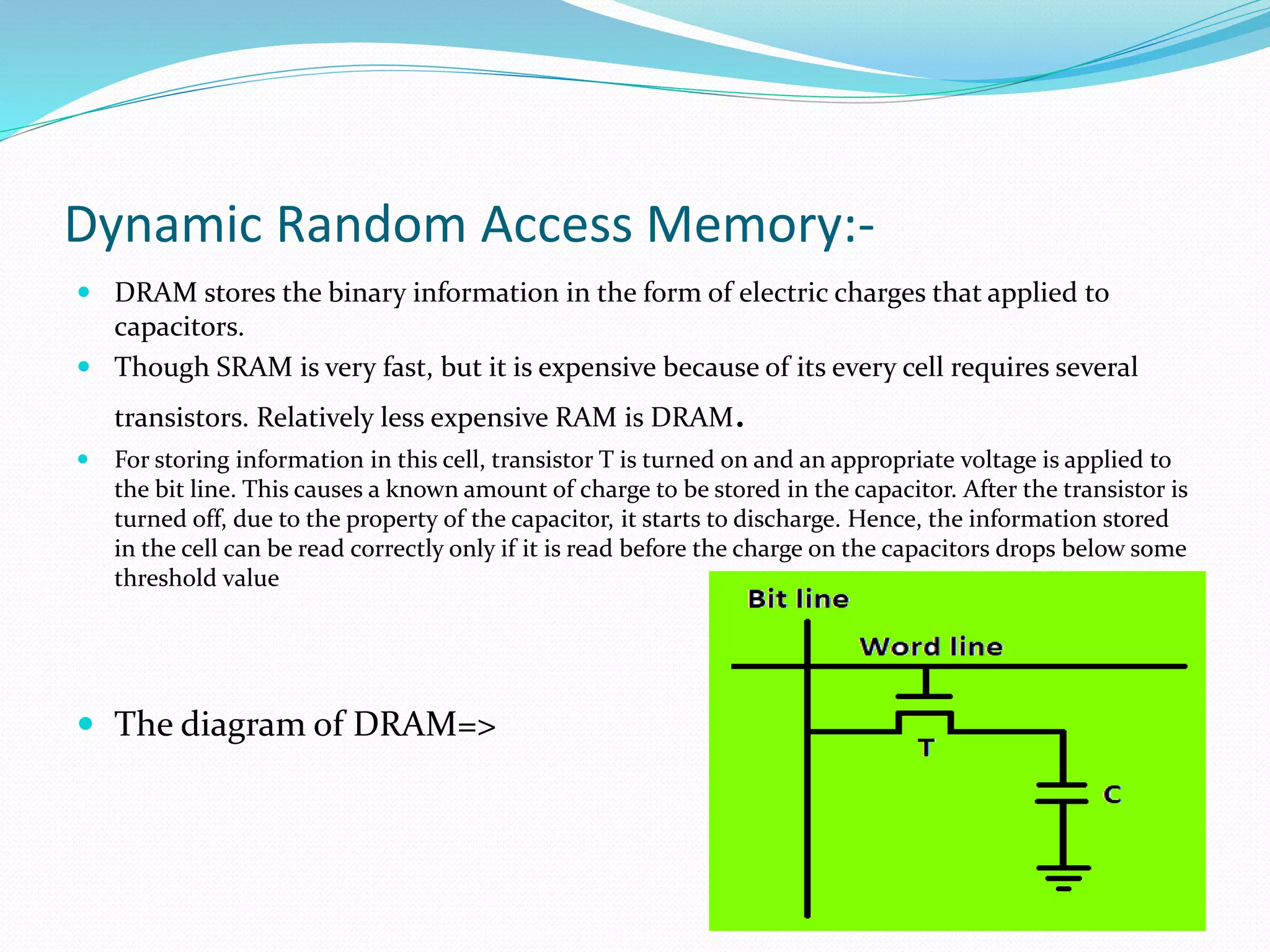

This document provides information about semiconductor RAM. It discusses the internal organization and types of RAM, including static RAM (SRAM) and dynamic RAM (DRAM). SRAM stores data using circuits that retain the information as long as power is applied, while DRAM uses capacitors to store electric charges representing data bits. The document outlines the read and write operations for each type and provides block diagrams of their internal structures. It concludes by noting some key differences between SRAM and DRAM.