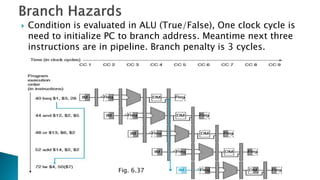

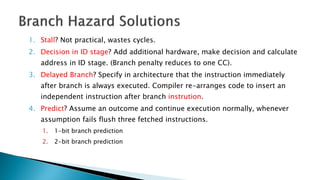

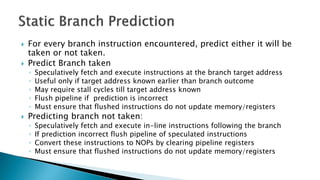

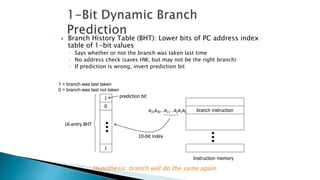

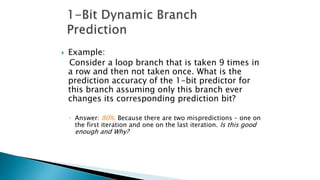

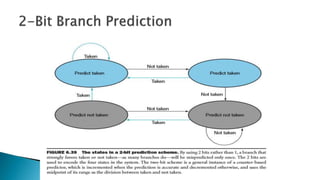

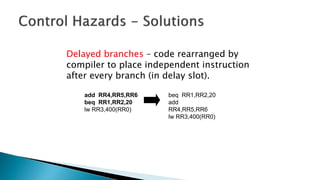

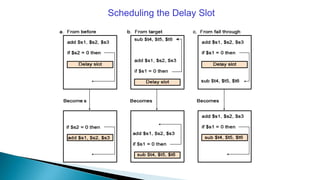

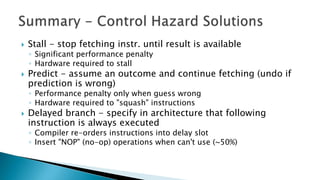

This document discusses different types of instruction hazards in pipelines including structural hazards, data hazards, and control hazards. It focuses on control hazards caused by branches, where the destination of the branch is unknown until it is evaluated. To resolve this, it discusses different branch prediction strategies like stalling, deciding the branch in the ID stage, delayed branches using compiler reordering, and branch prediction. Branch prediction involves using a branch history table (BHT) to predict if the branch will be taken or not based on its past behavior. The document provides statistics on typical branch behavior and analyzes the accuracy of 1-bit branch prediction. It also discusses scheduling instructions into the delay slot of delayed branches.