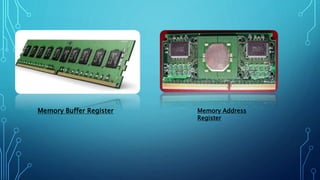

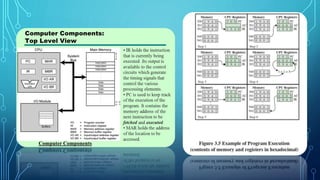

The document discusses program execution in the central processing unit (CPU). It explains that the CPU fetches instructions from memory one at a time and executes them using its control unit, arithmetic logic unit, and registers. The execution process involves fetching the instruction from memory into the instruction register, decoding what type of instruction it is, executing the appropriate operation using components like the accumulator and memory address register, and storing the output, which may update the program counter. Key components like the control unit, registers, and arithmetic logic unit work together to precisely carry out the steps specified in the stored program.