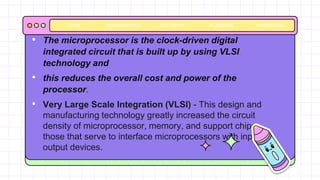

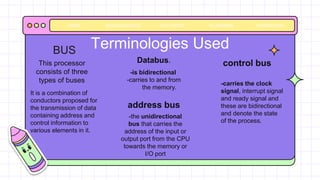

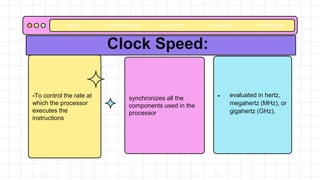

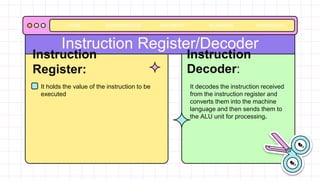

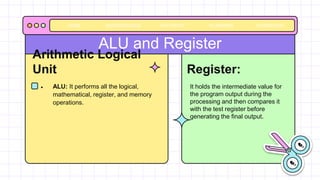

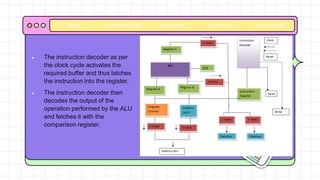

The document discusses microprocessor systems. It defines a microprocessor as a small computation unit fabricated on a single chip that serves as the central processing unit of computers and other electronic systems. It explains that microprocessors use VLSI technology to integrate various components like the ALU, registers, and control unit onto a single chip. This allows microprocessors to be smaller, faster, and less expensive than earlier circuit-based CPUs. The document also provides block diagrams and descriptions of typical microprocessor components and their functions.