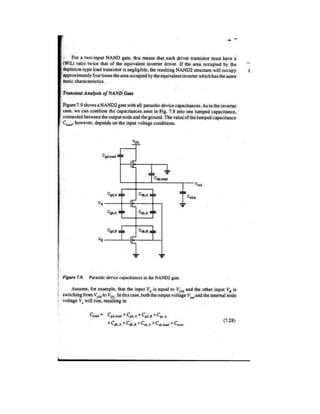

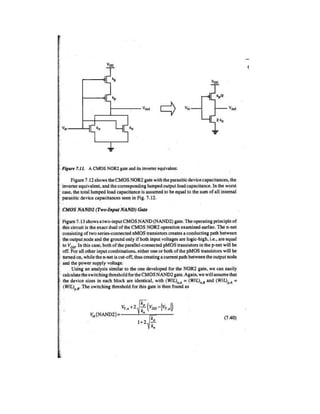

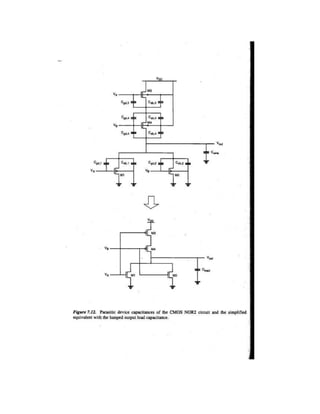

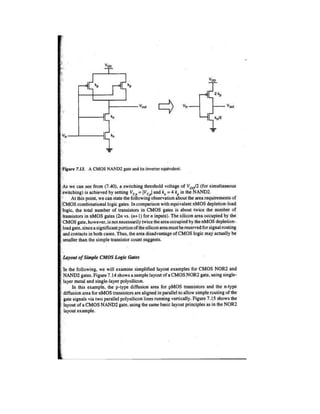

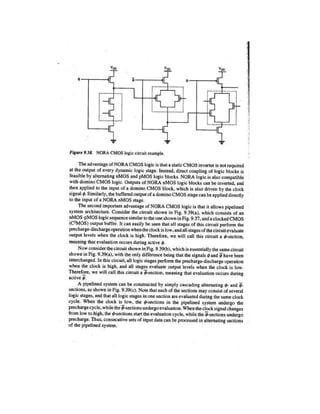

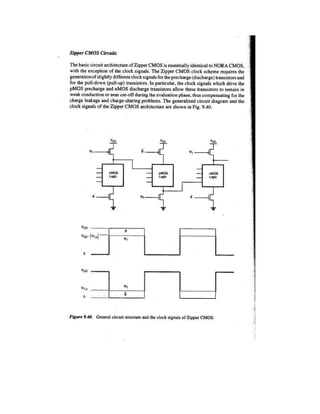

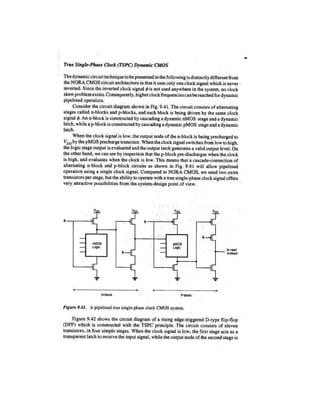

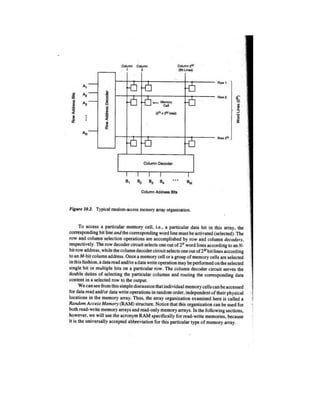

This document provides lecture notes for a course on CMOS digital IC design. The course objectives are to discuss CMOS logic gates, implementation of AOI and OAI gates, design of logic circuits using transmission gates, analysis of delays and power dissipation in combinational circuits, and design of combinational circuits using different logic styles. The document outlines 5 units that will be covered: MOS design, combinational MOS logic circuits, sequential MOS logic circuits, dynamic logic circuits, and semiconductor memories. It lists textbooks and references and describes the expected course outcomes as being able to apply transistor physics in CMOS circuit analysis, design CMOS inverters meeting noise margins, execute moderately sized logic designs using various gates, and design