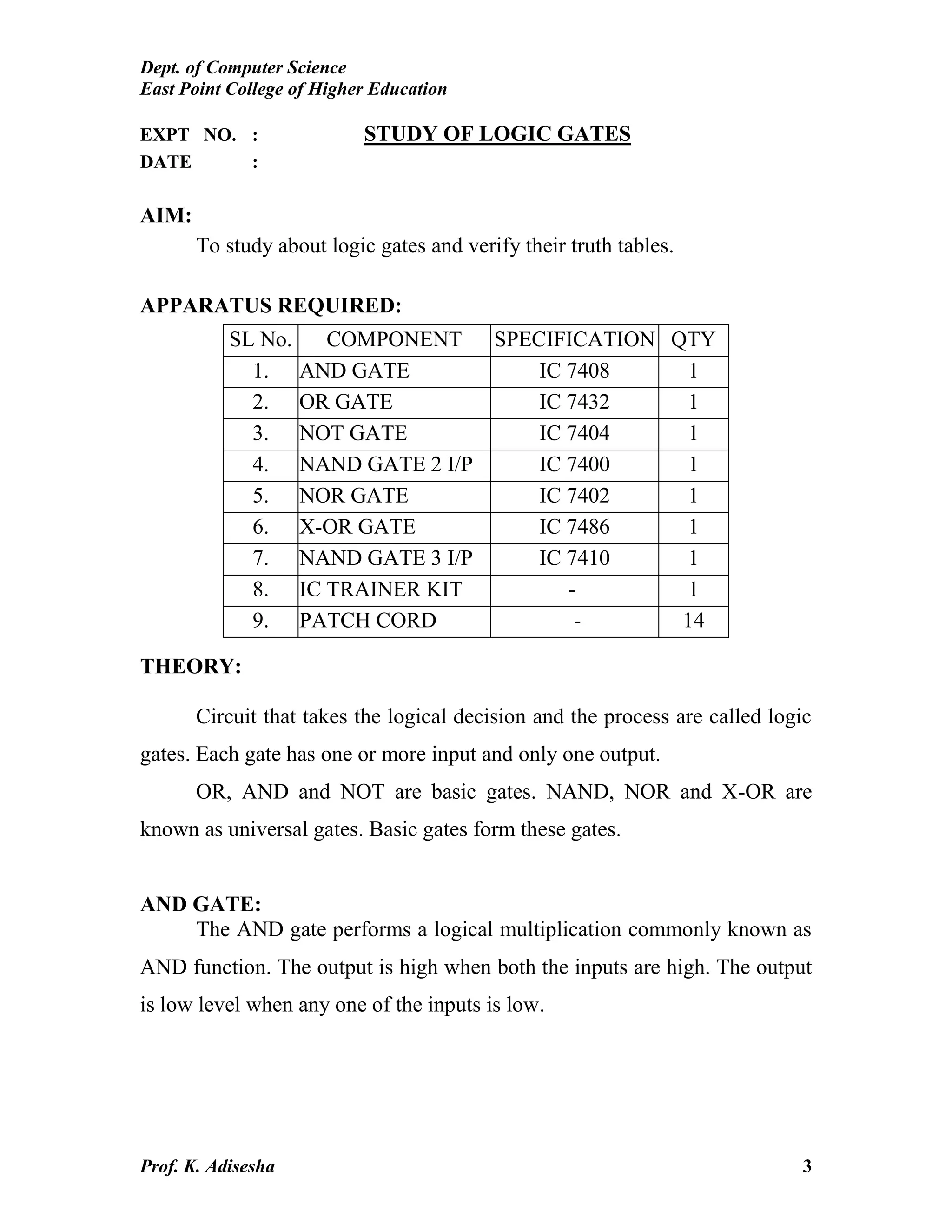

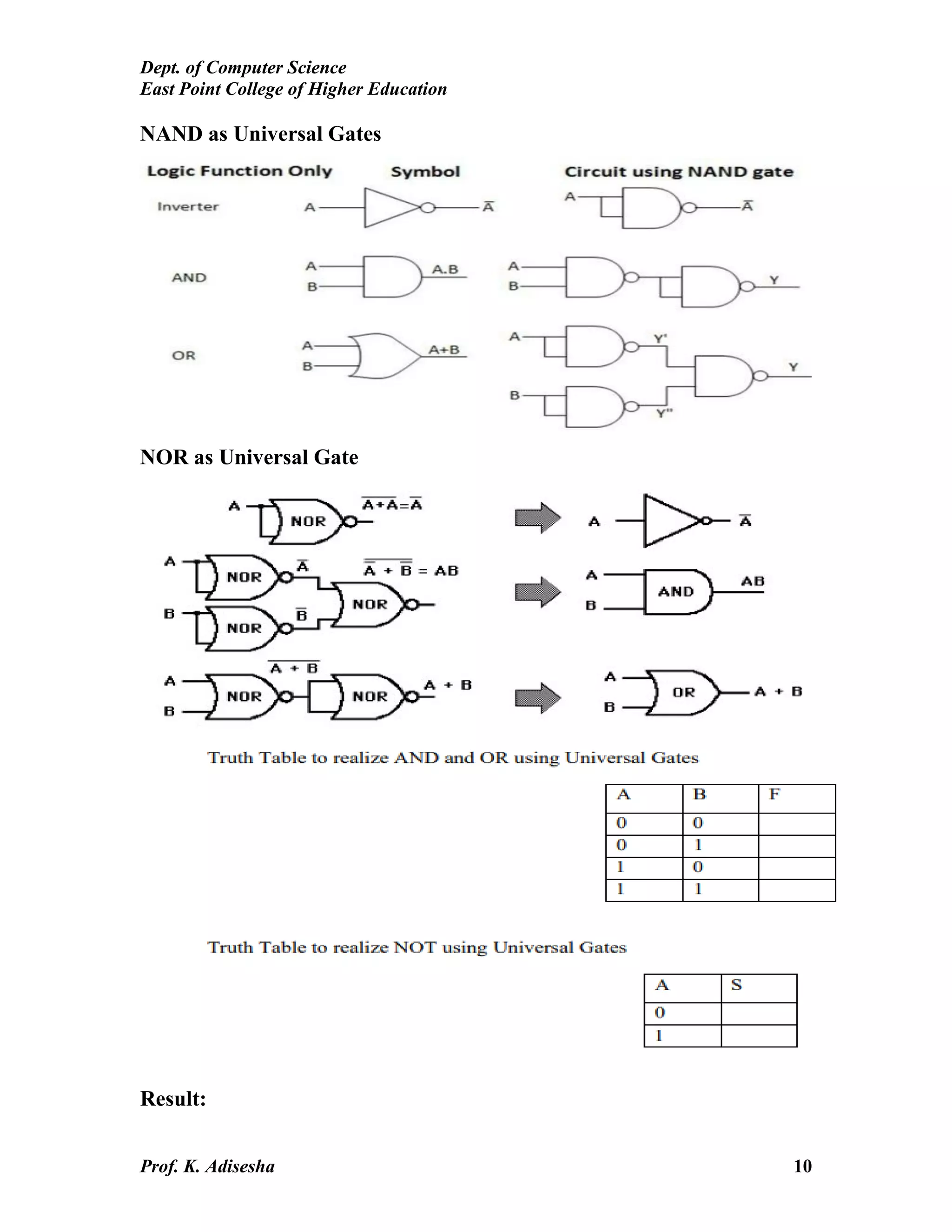

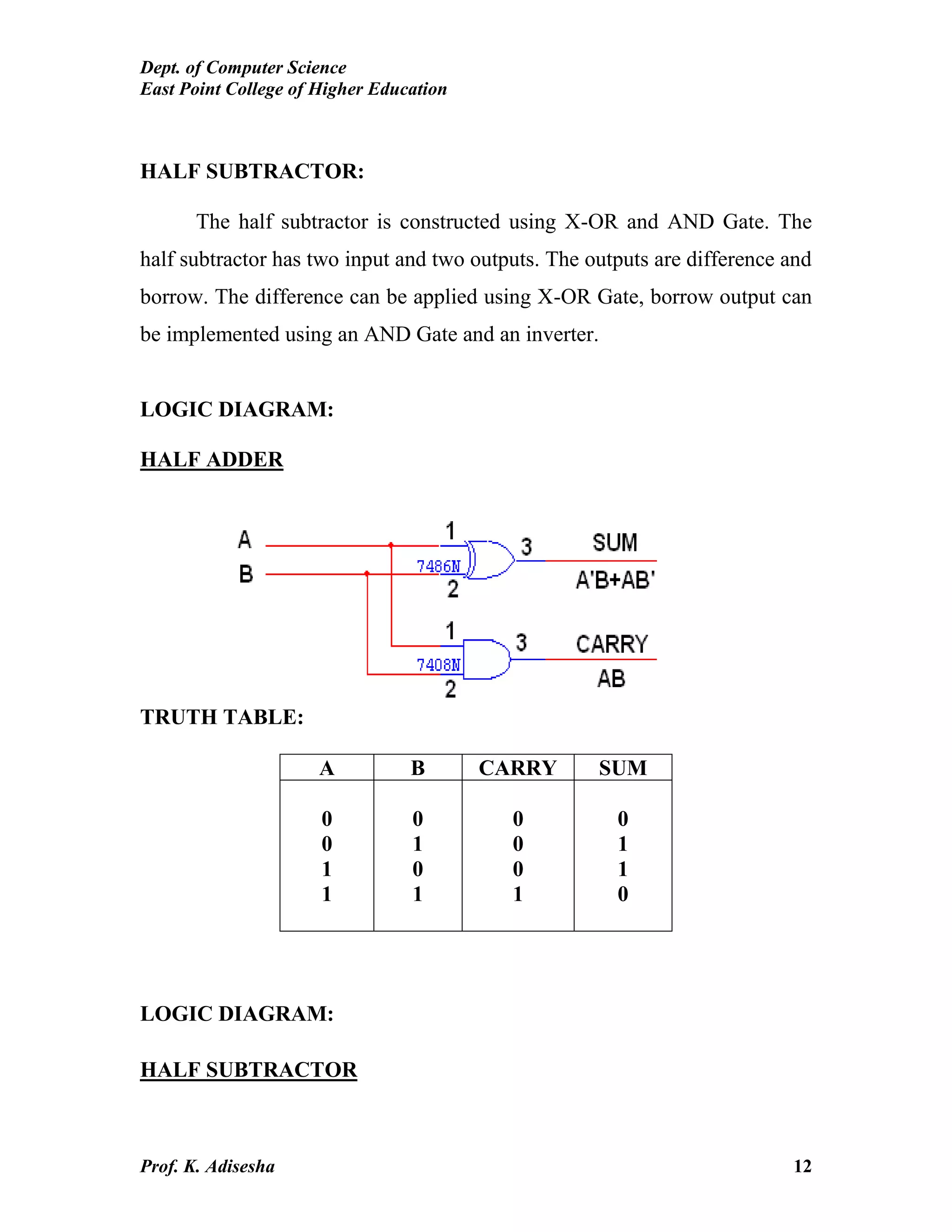

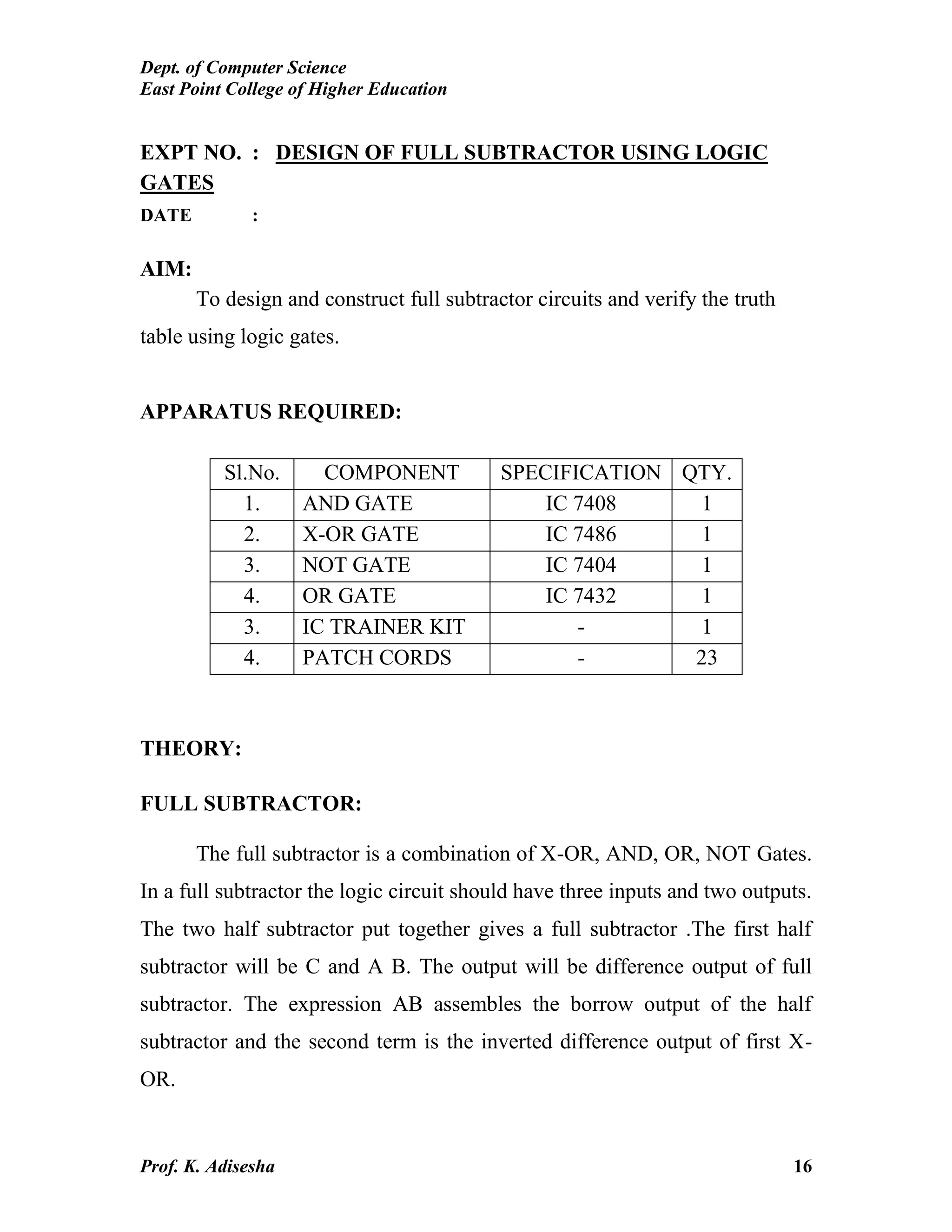

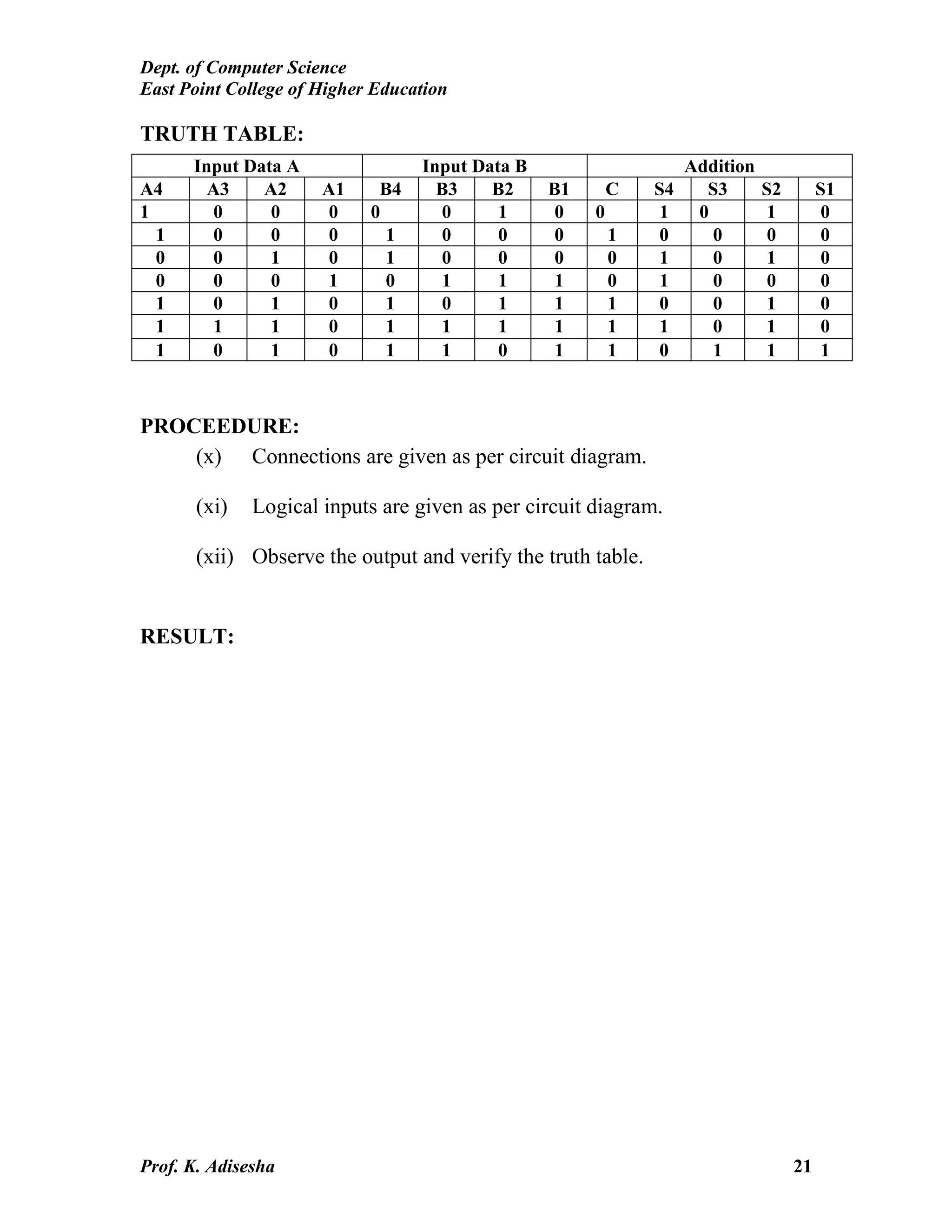

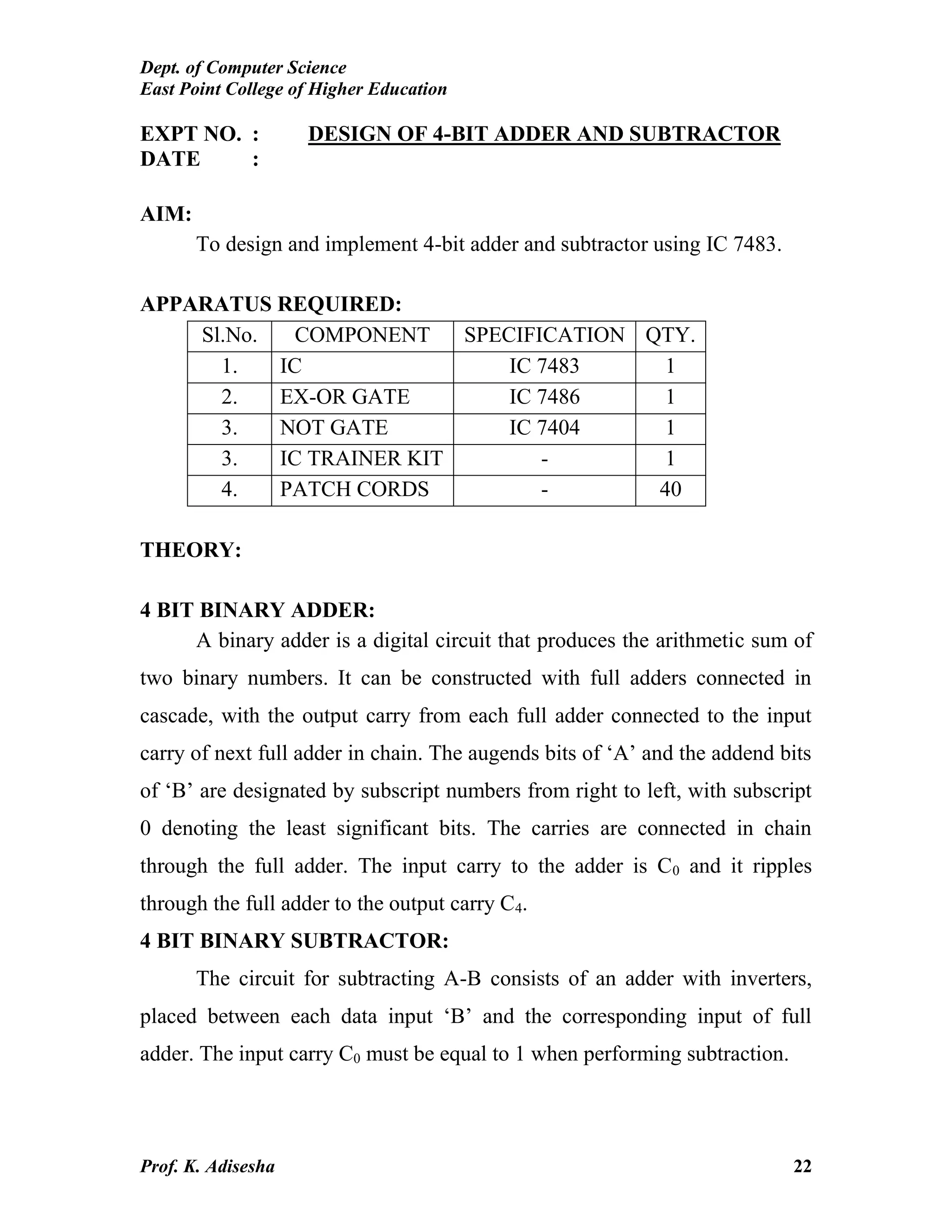

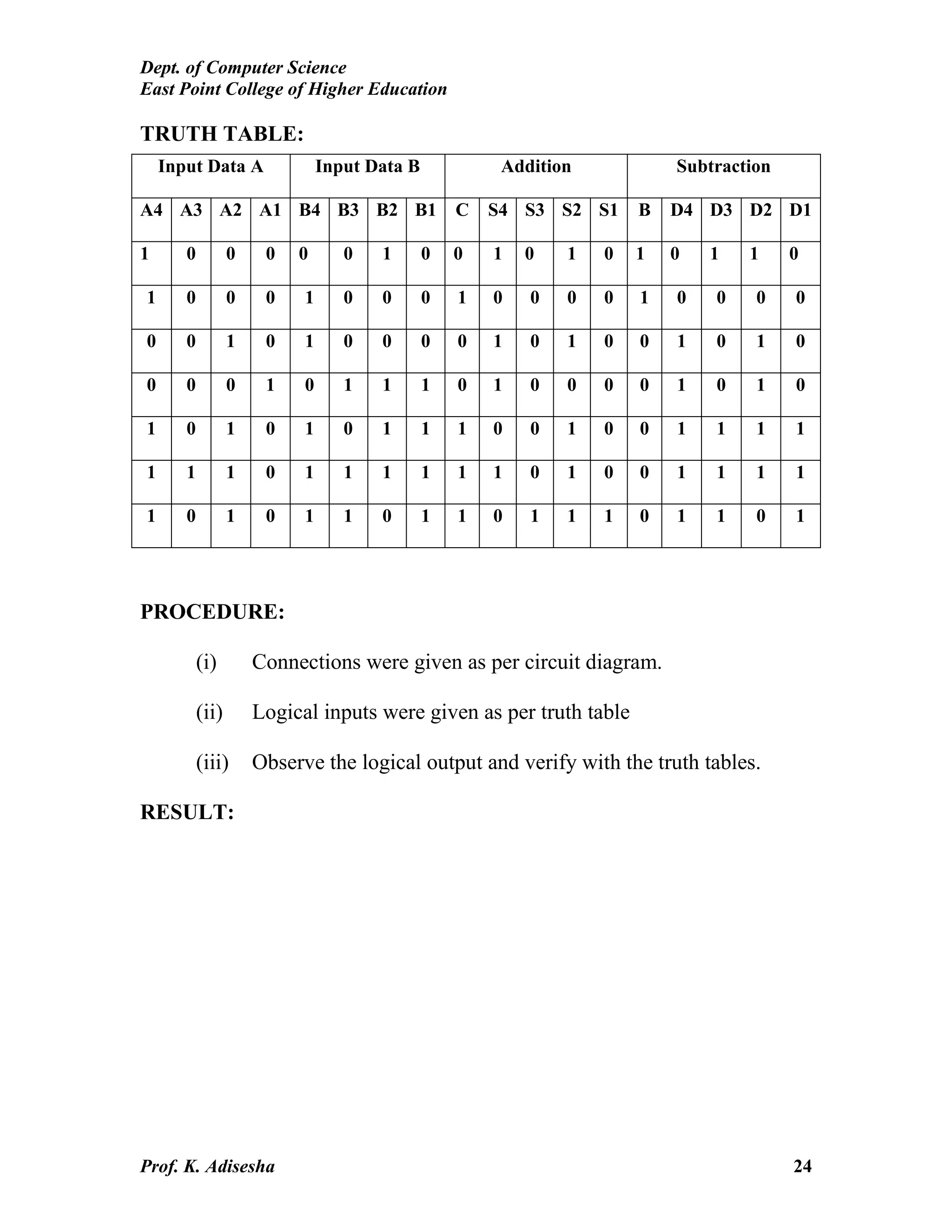

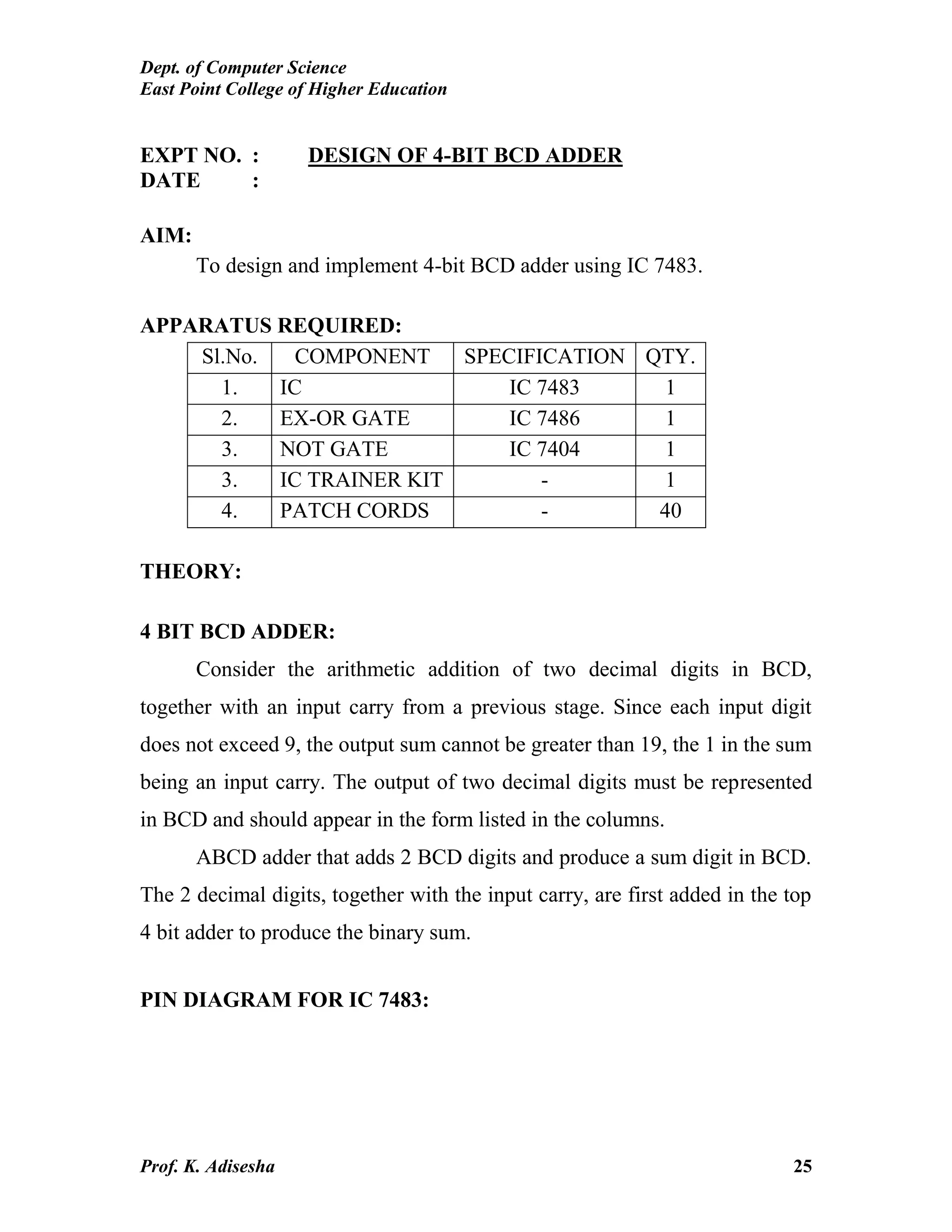

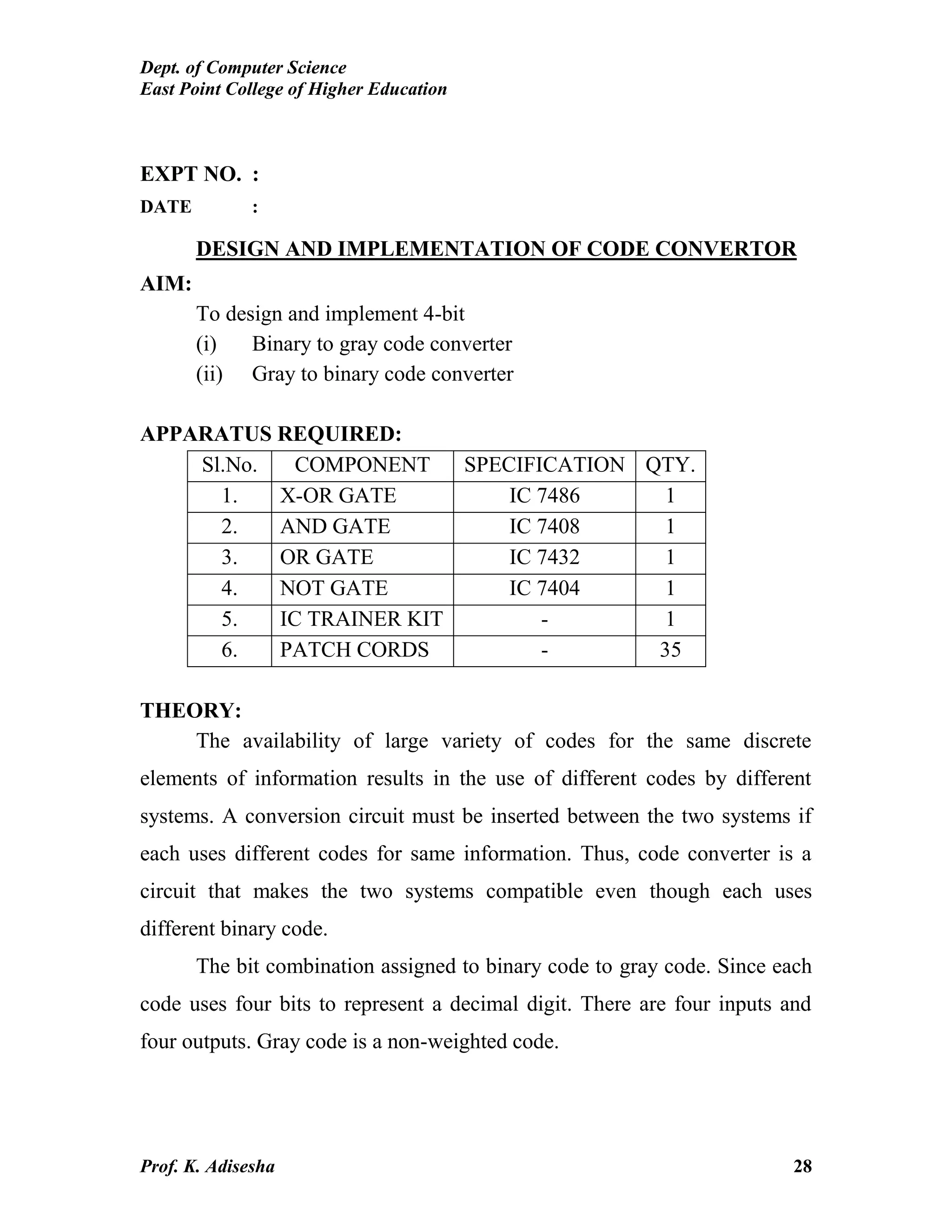

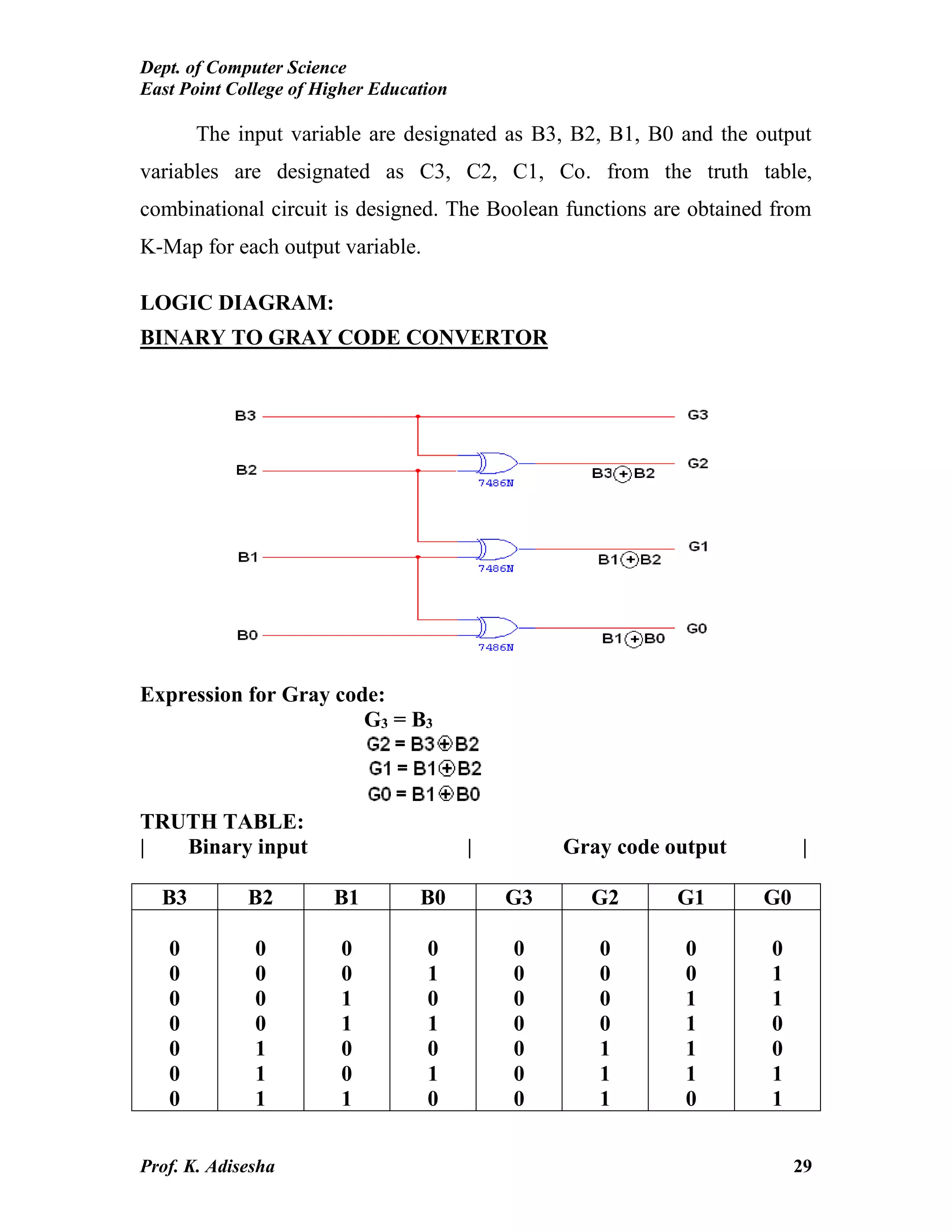

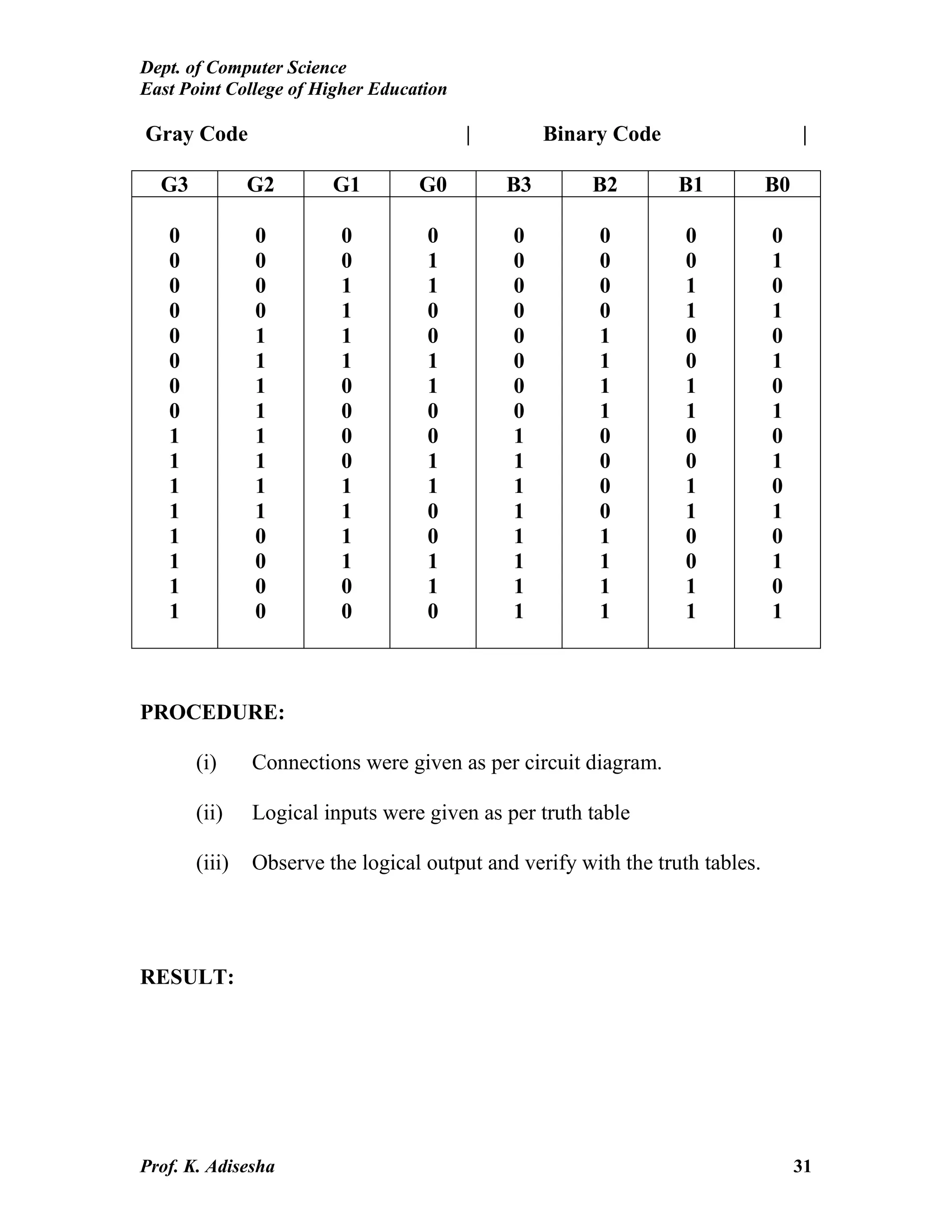

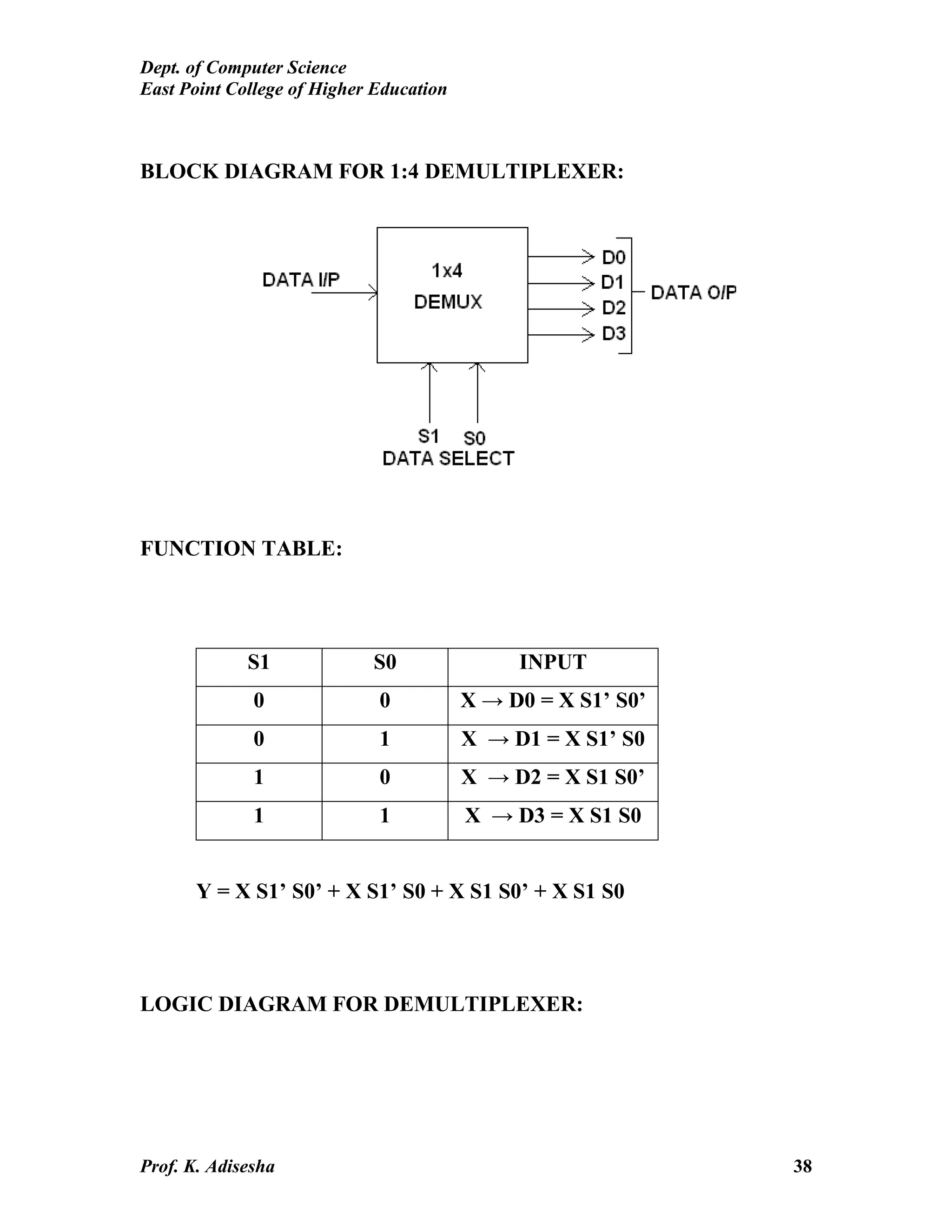

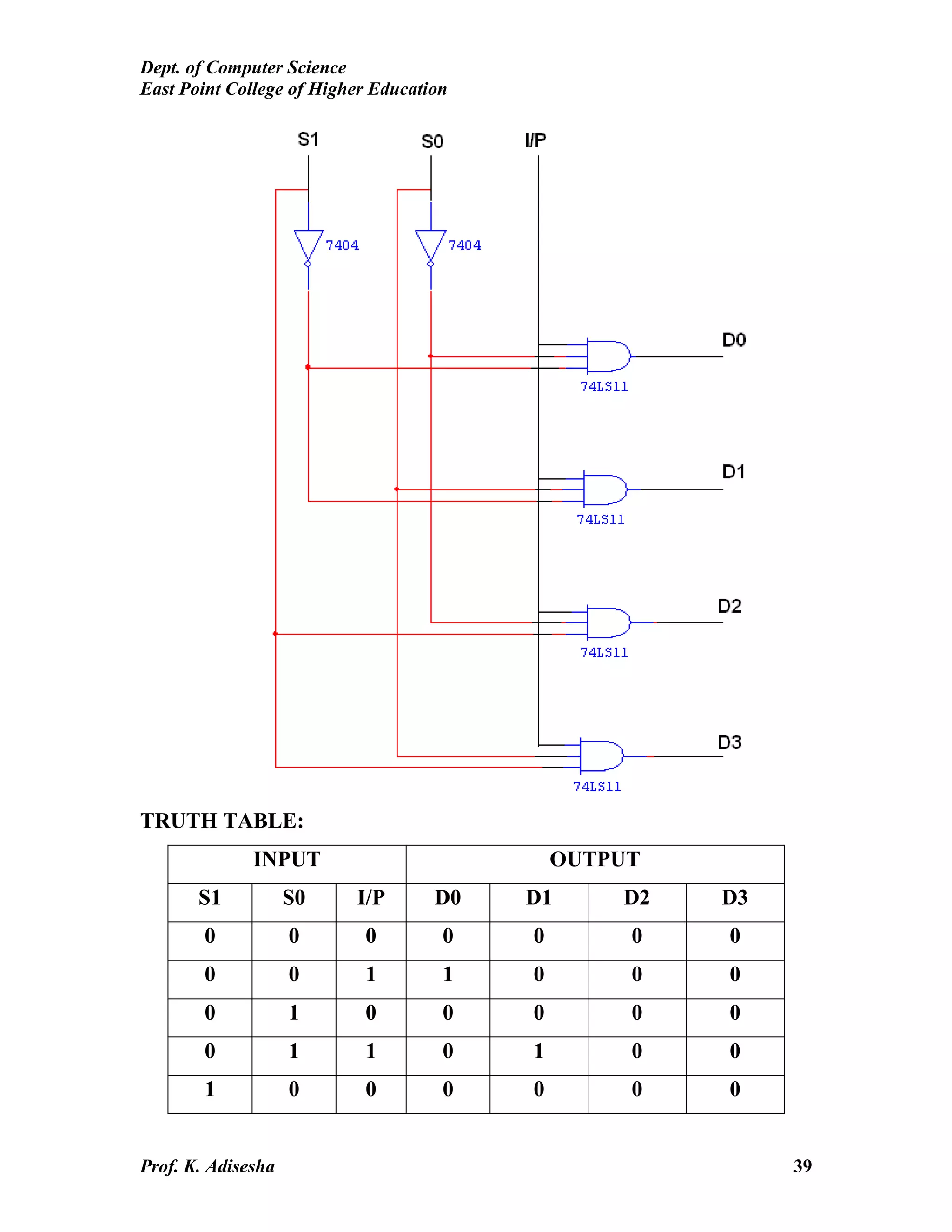

This document contains the lab manual for a digital electronics course. It outlines 10 experiments involving logic gates and circuits, including studying logic gates, universal gates, half and full adders/subtractors using logic gates, and designing 4-bit adders and subtractors using the IC 7483. The experiments are meant to help students learn about basic digital logic components and how to design circuits using gates to perform arithmetic operations like addition and subtraction.