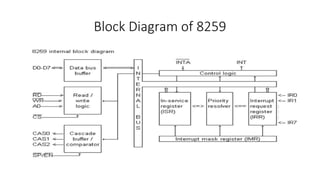

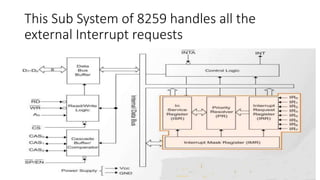

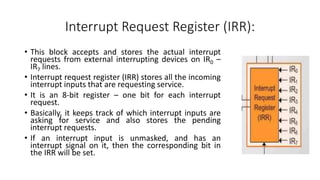

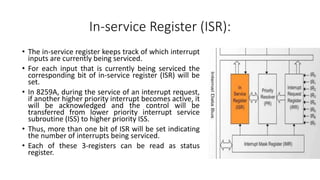

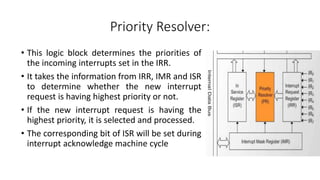

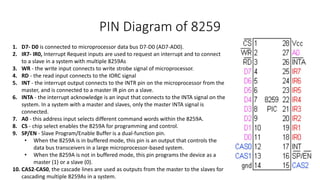

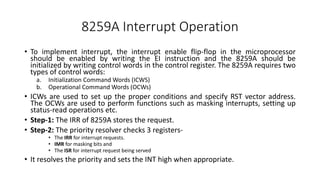

The 8259A Programmable Interrupt Controller (PIC) handles prioritized interrupt requests from peripherals for the CPU. It accepts up to 8 interrupt requests, determines priority, and issues an interrupt to the CPU. It can be programmed and cascaded to handle more interrupts. The PIC includes registers to store incoming requests, mask bits, and service status. It uses initialization and operation command words to configure operation and interact with the CPU through control signals and data bus.