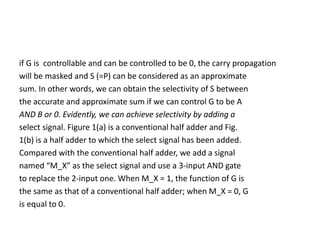

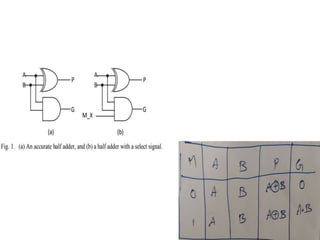

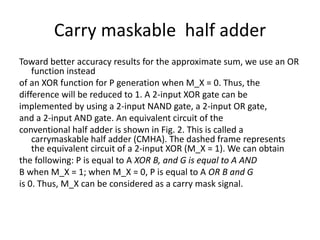

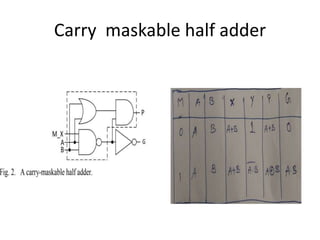

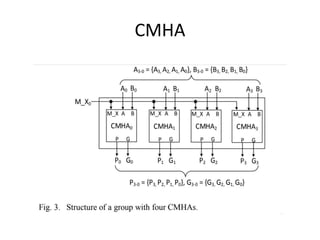

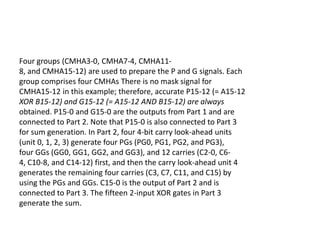

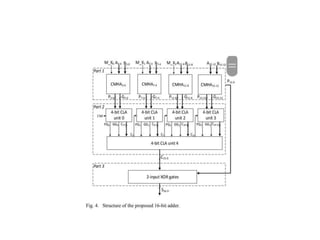

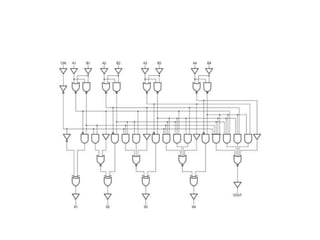

This presentation proposes a new carry maskable look ahead adder design that combines carry look ahead adders with carry masking to improve adder performance for approximate computing. It works by masking the carry propagation through a carry mask signal to optionally make the adder faster but less accurate. The proposed adder architecture has three parts: carry generation, carry look ahead units, and sum generation using XOR gates. It aims to reduce propagation delay, chip area, and circuit complexity compared to conventional carry look ahead adders.