Embed presentation

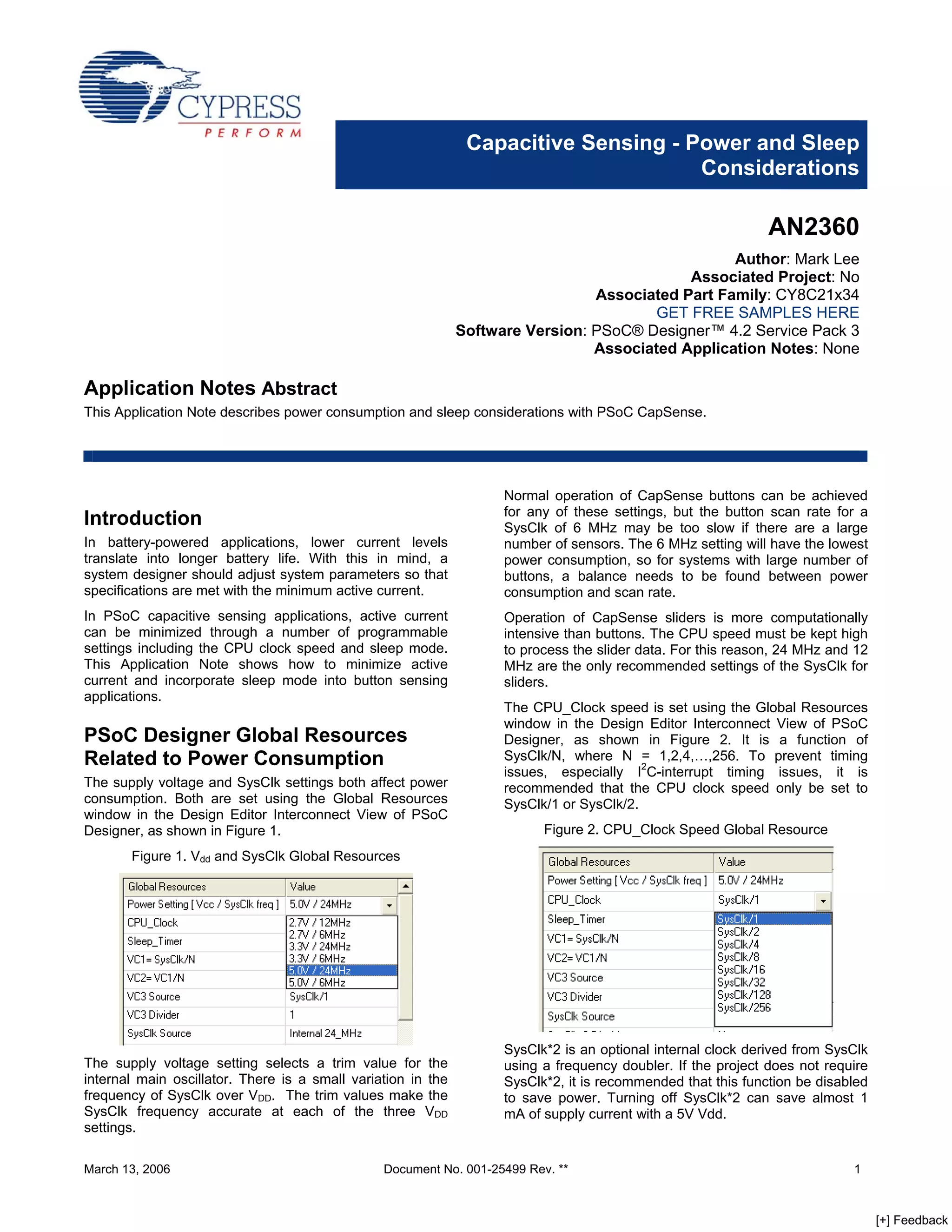

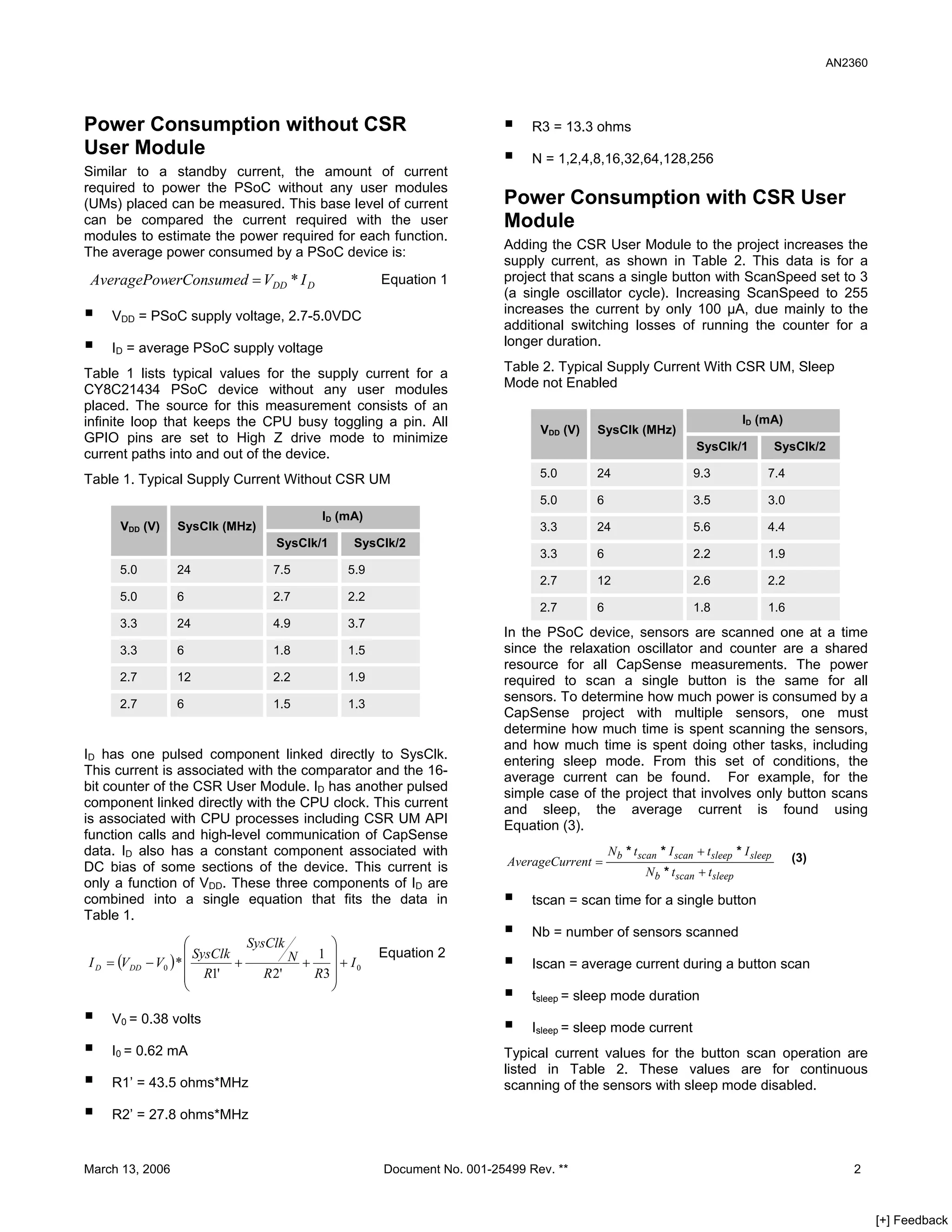

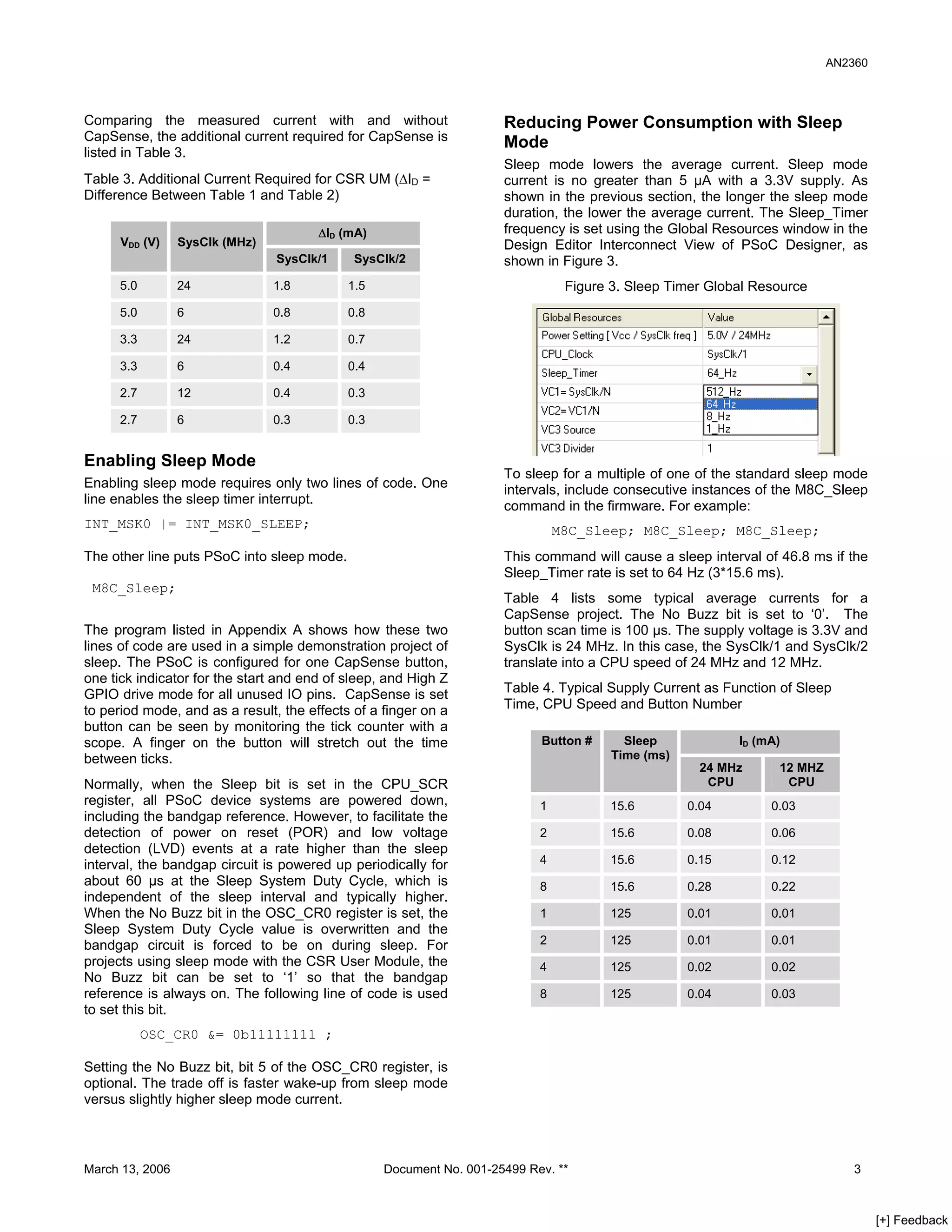

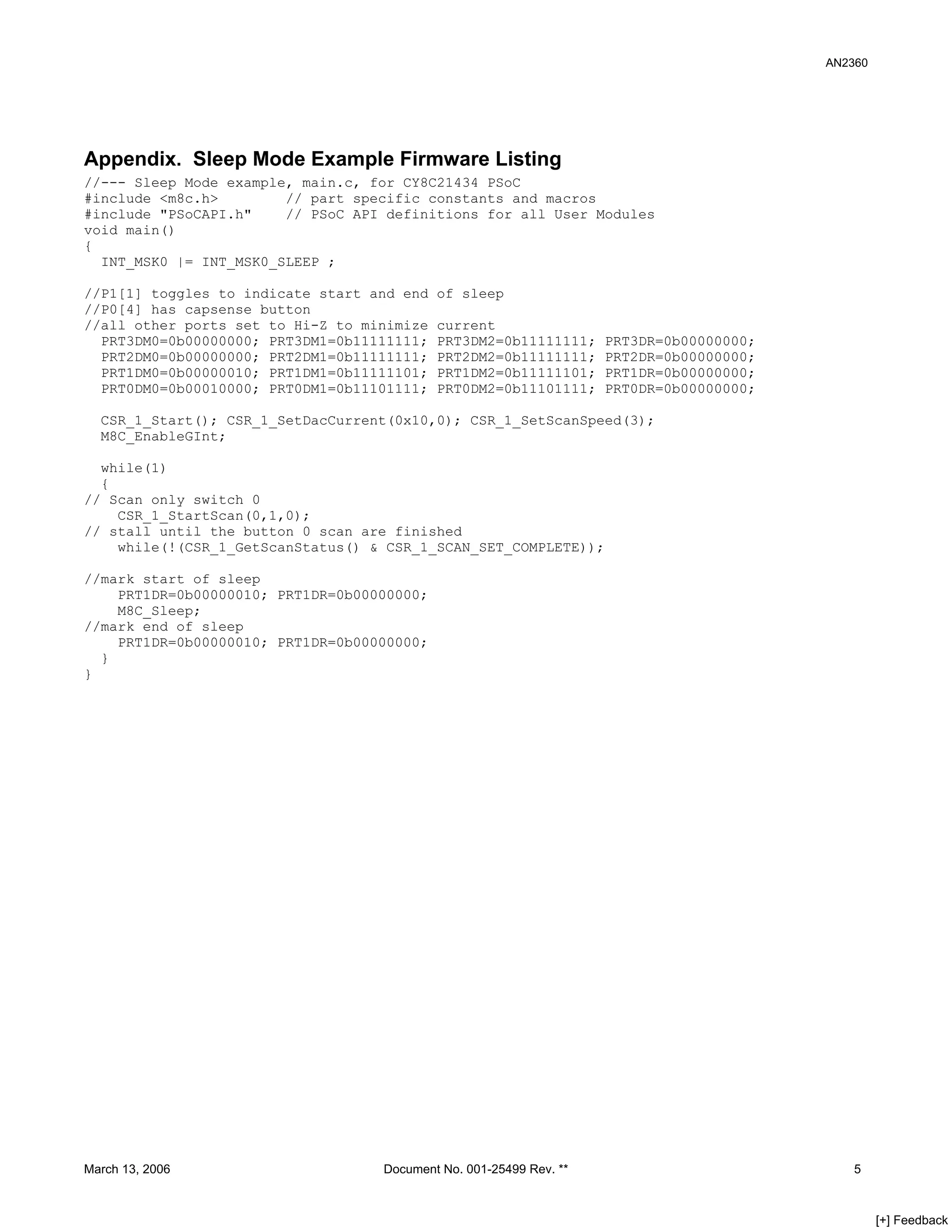

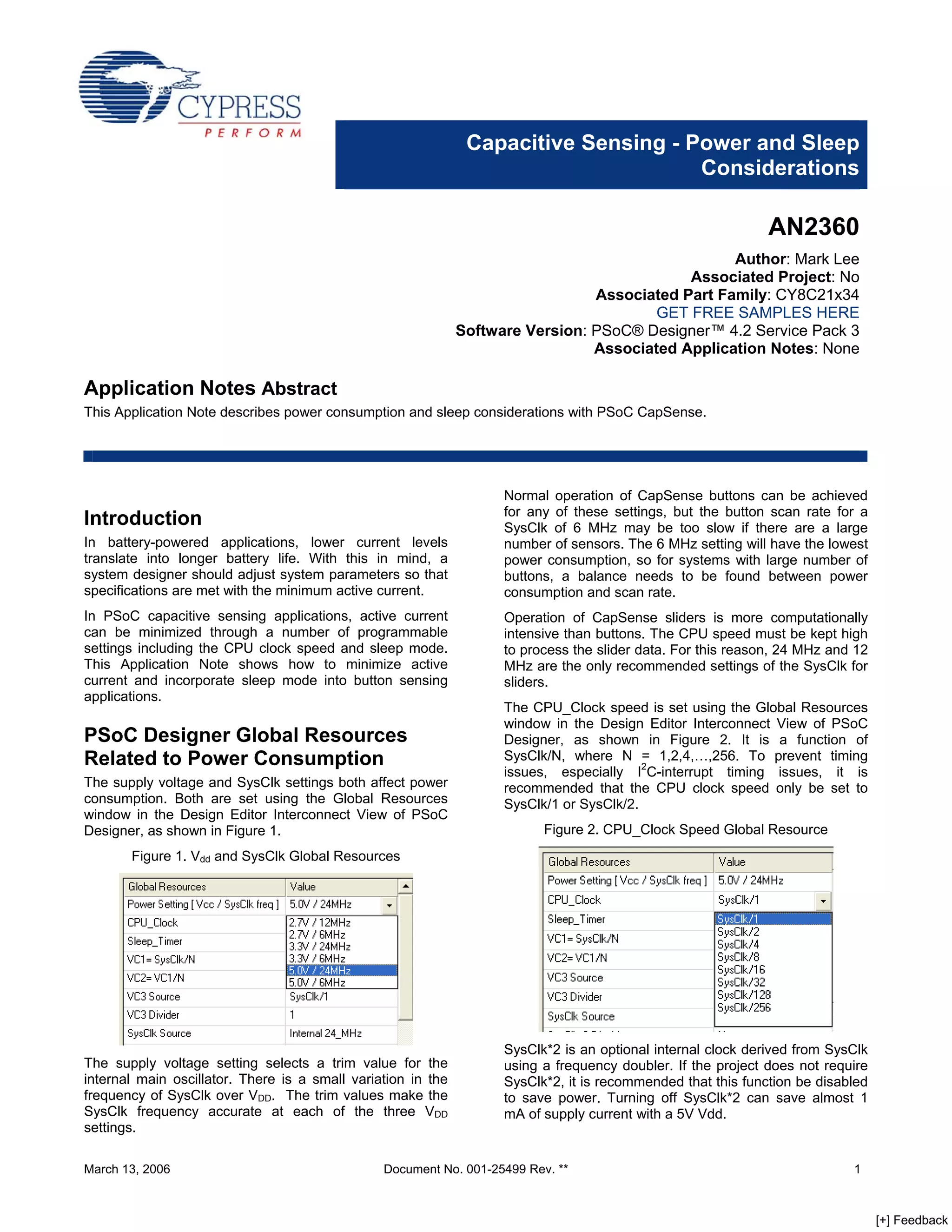

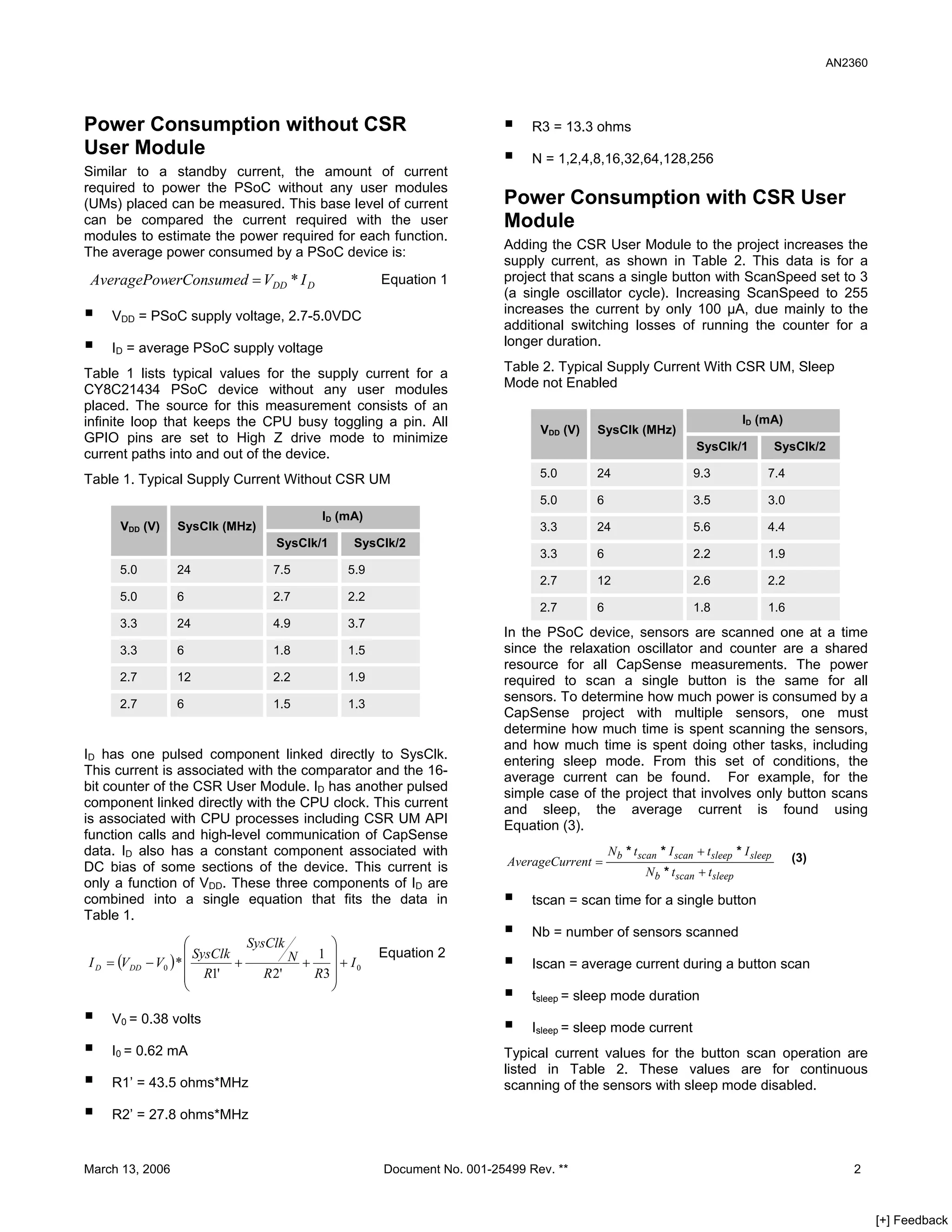

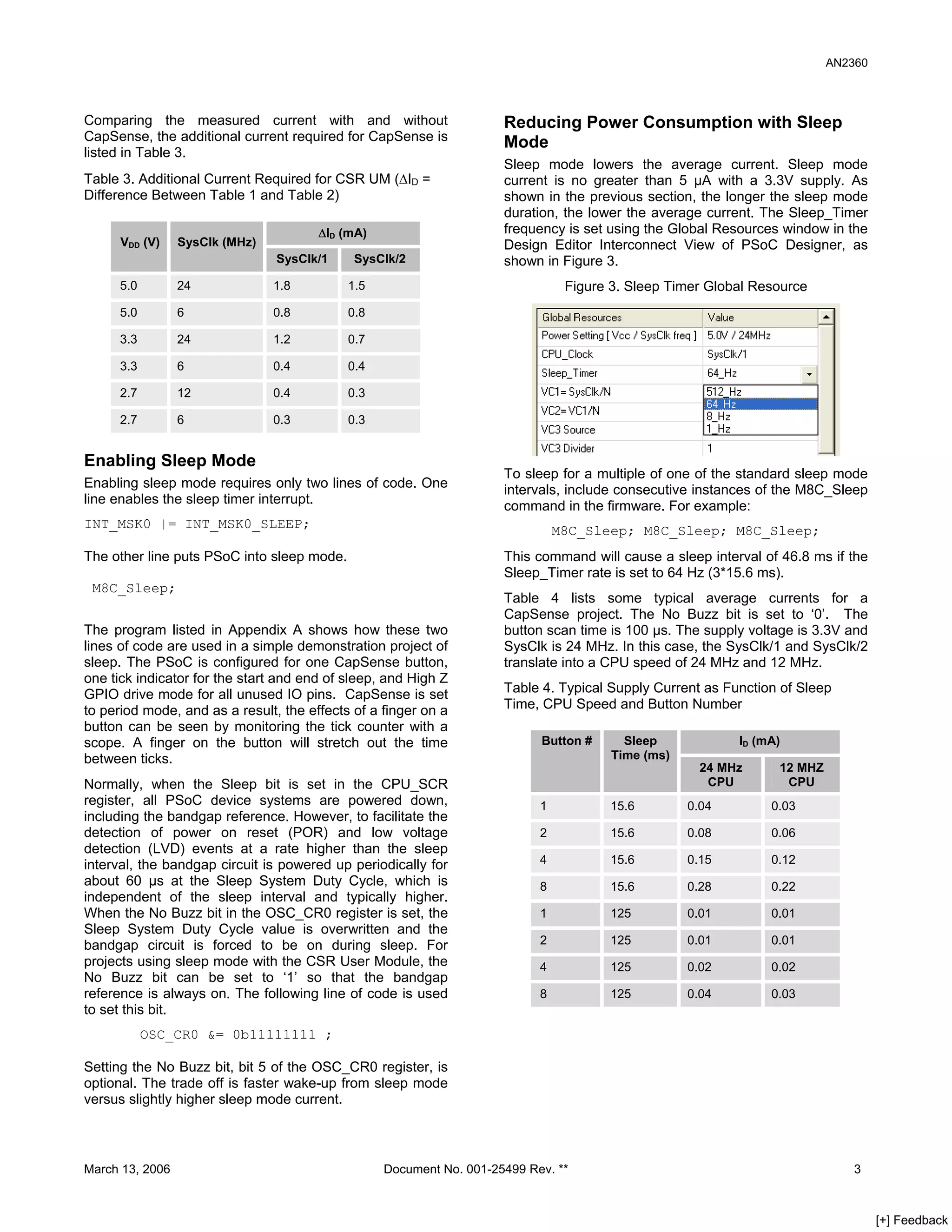

This application note discusses power and sleep considerations for PSoC capacitive sensing (CapSense) applications, emphasizing the balance between active current and scan rate for battery-operated devices. Key factors affecting power consumption include CPU speed, supply voltage, and the number of sensors scanned, with detailed design equations provided to help optimize performance. The note also explains how implementing sleep mode can effectively extend battery life, allowing for minor firmware adjustments to achieve efficient operation.