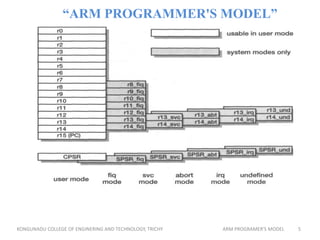

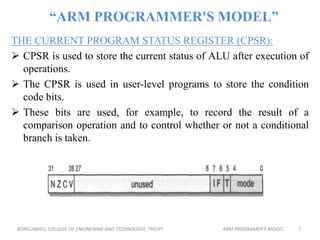

The document presents an overview of the ARM programmer's model, detailing its architecture, register types, and functionality. It explains the significance of special function registers like the stack pointer, link register, and program counter, along with the current program status register (CPSR) used for condition codes. The conclusion summarizes the key concepts of the ARM model, registers, and CPSR in the context of microcontroller system design.