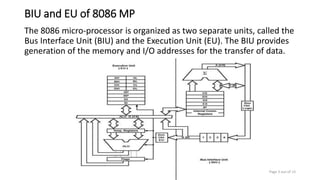

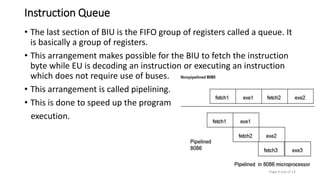

The document provides an overview of the Bus Interface Unit (BIU) of the 8086 microprocessor, detailing its role in data and address transfer for the Execution Unit (EU). It describes various components of the BIU including the instruction queue, segment registers, and the instruction pointer, along with their functions in program execution. The BIU enables efficient data handling through techniques like pipelining to speed up instruction processing.