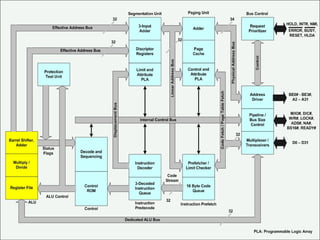

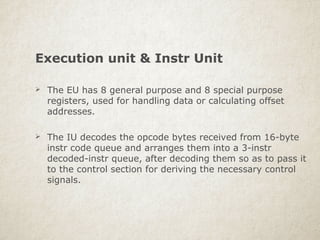

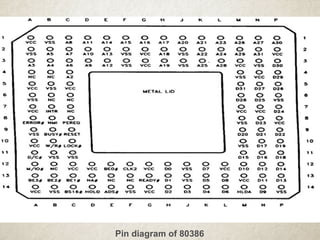

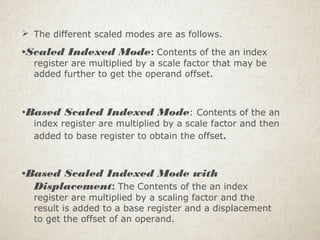

This document describes the architecture of the 8086 microprocessor. It includes descriptions of the main components: the central processing unit containing the execution unit, instruction unit, memory management unit, and bus interface unit. It then provides details on the execution unit, instruction unit, memory management unit, addressing modes, pin diagram, and references used.