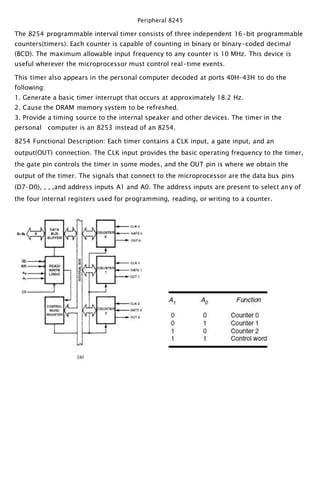

The 8254 programmable interval timer consists of three independent 16-bit programmable counters that can each count in binary or BCD up to a maximum frequency of 10 MHz. This timer is useful for controlling real-time events in microprocessors. In personal computers, the timer generates an 18.2 Hz interrupt, refreshes DRAM memory, and provides timing to devices like speakers. Each counter has inputs and outputs to control counting. The 8254 has various modes to generate pulses, squares waves, and one-shots using the counters.