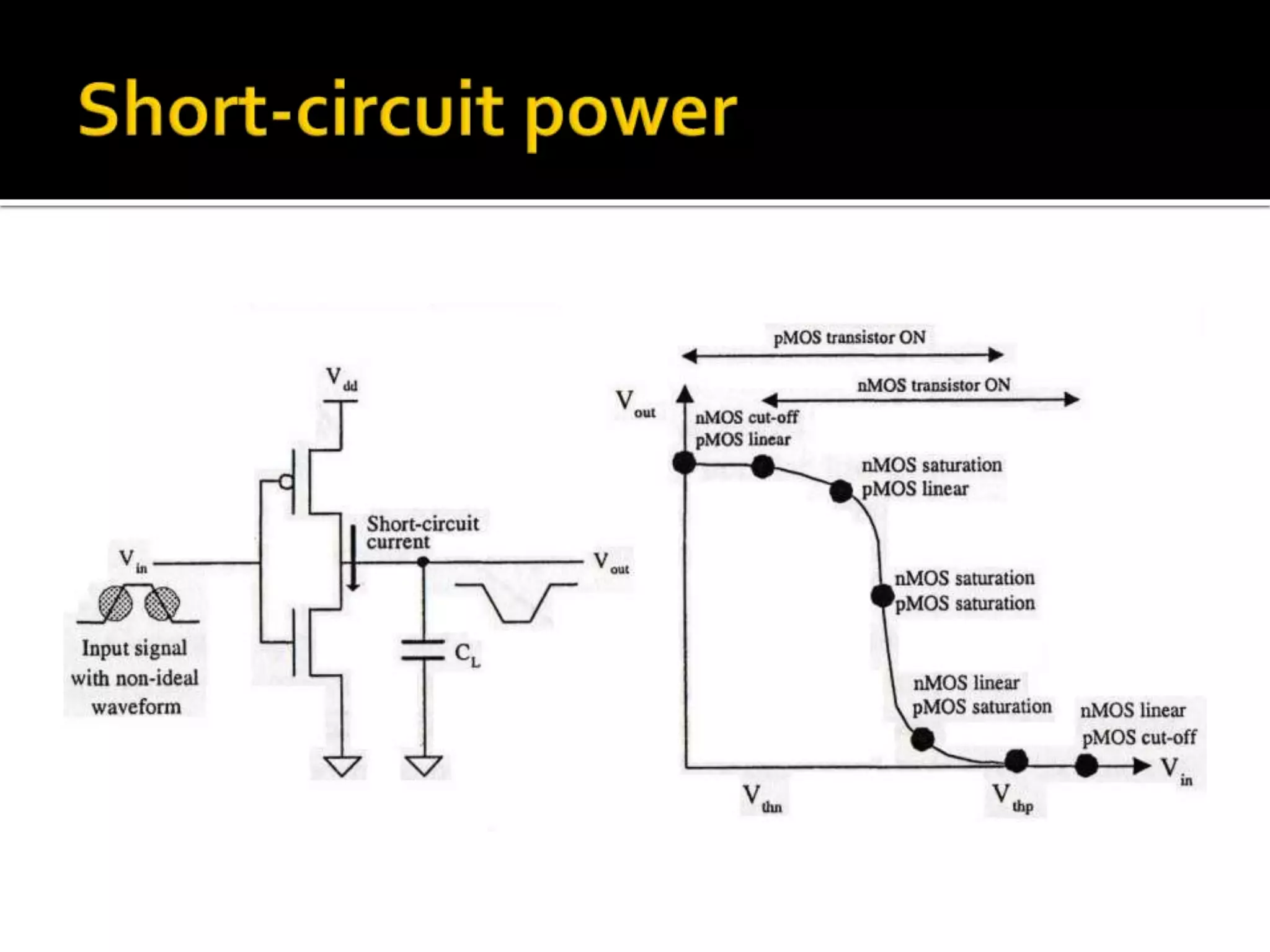

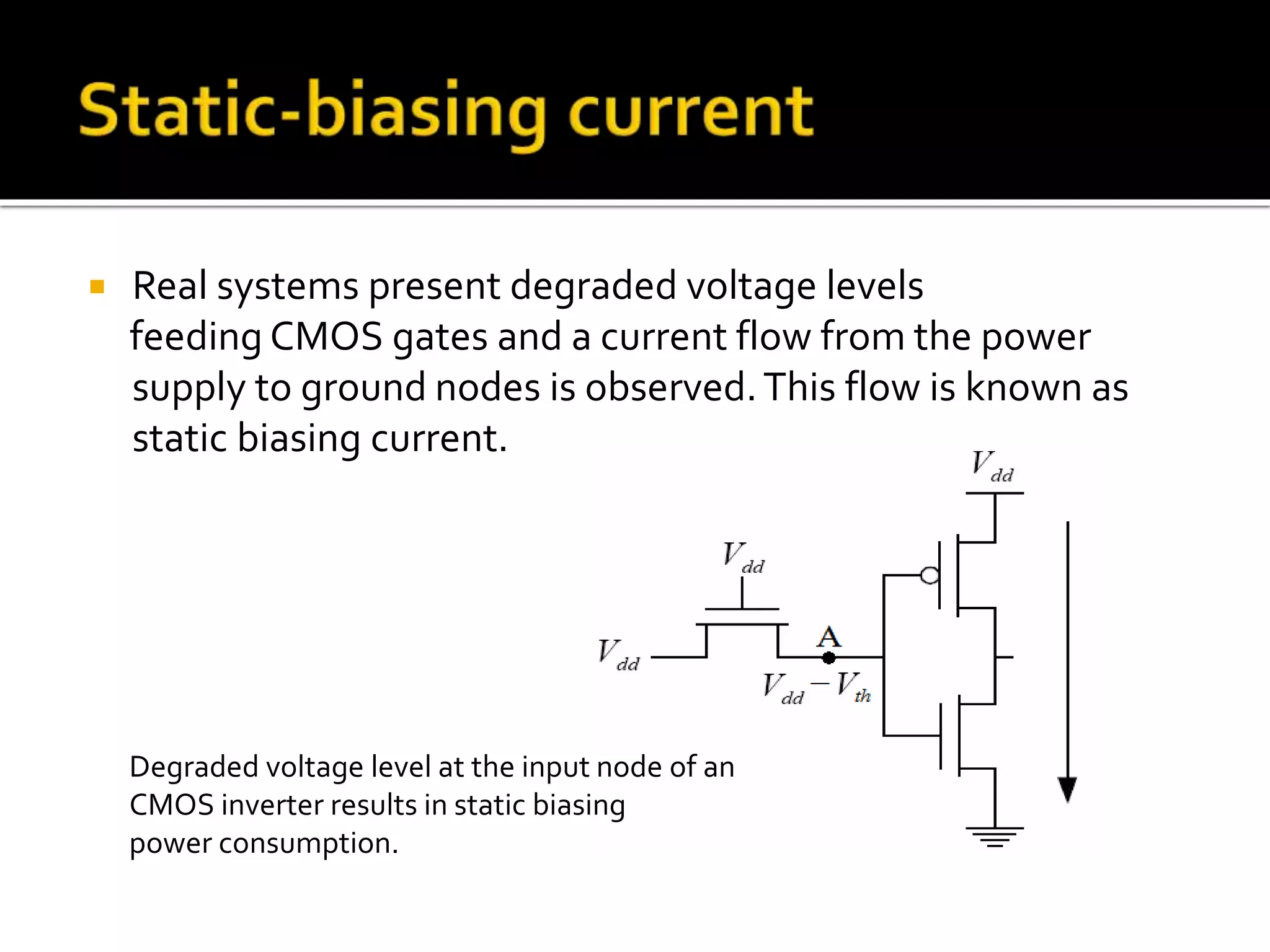

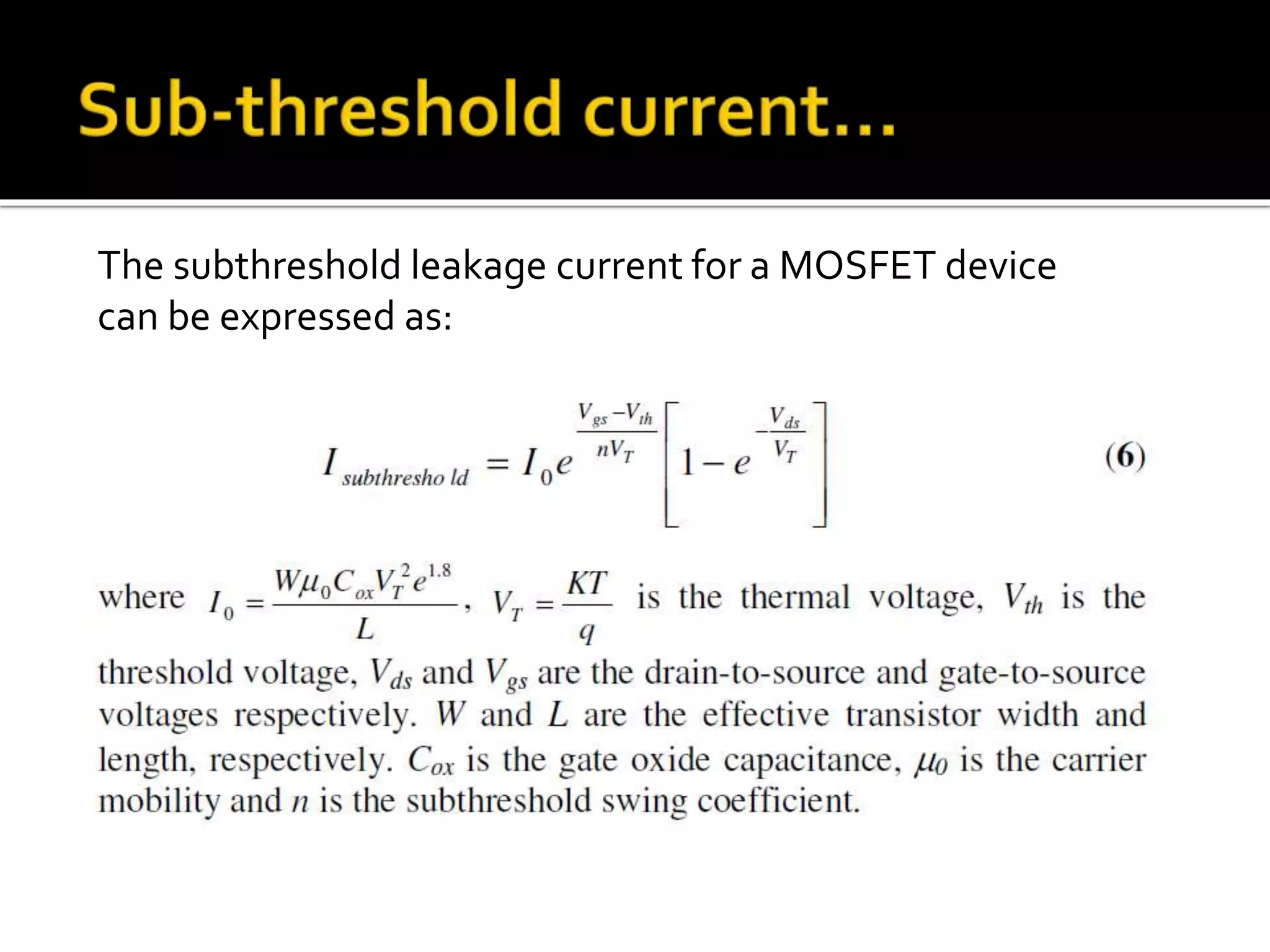

The document discusses power dissipation in digital CMOS circuits, highlighting dynamic switching power as the dominant component for technologies up to 0.18μm, accounting for around 90% of total dissipation. It also details the types of power dissipation including short-circuit current, static biasing, and leakage mechanisms, such as subthreshold and band-to-band tunneling. The impacts of technology scaling on power consumption, particularly with regard to transistor threshold voltage and oxide thickness, are examined, noting the challenges posed by increased leakage currents in low-power designs.