VHDL CODE

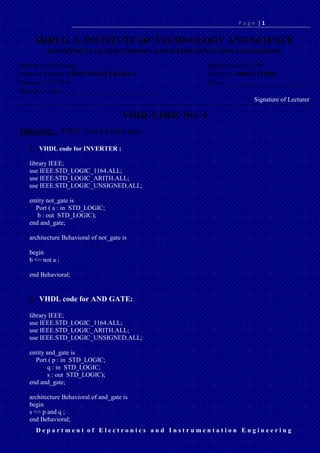

- 1. P a g e | 1 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 1 Objective: - VHDL code for logic gate. 1. VHDL code for INVERTER : library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity not_gate is Port ( a : in STD_LOGIC; b : out STD_LOGIC); end and_gate; architecture Behavioral of not_gate is begin b <= not a ; end Behavioral; 2. VHDL code for AND GATE: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity and_gate is Port ( p : in STD_LOGIC; q : in STD_LOGIC; s : out STD_LOGIC); end and_gate; architecture Behavioral of and_gate is begin s <= p and q ; end Behavioral;

- 2. P a g e | 2 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 3. VHDL code for OR GATE : library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity or_gate is Port ( p : in STD_LOGIC; q : in STD_LOGIC; s : out STD_LOGIC); end or_gate; architecture Behavioral of or_gate is begin s <= p or q ; end Behavioral; 4. VHDL code for NAND GATE : library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity nand_gate is Port ( p : in STD_LOGIC; q : in STD_LOGIC; s : out STD_LOGIC); end nand_gate; architecture Behavioral of nand_gate is begin s <= p nand q ; end Behavioral;

- 3. P a g e | 3 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 5. VHDL code for NOR GATE: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity nor_gate is Port ( p : in STD_LOGIC; q : in STD_LOGIC; s : out STD_LOGIC); end nor_gate; architecture Behavioral of nor_gate is begin s <= p nor q ; end Behavioral; 6. VHDL code for Ex-OR GATE: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity xor_gate is Port ( p : in STD_LOGIC; q : in STD_LOGIC; s : out STD_LOGIC); end xor_gate; architecture Behavioral of xor_gate is begin s <= p xor q ; end Behavioral; 7. VHDL code for EX_NOR : library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity xnor_gate is Port ( p : in STD_LOGIC; q : in STD_LOGIC; s : out STD_LOGIC);

- 4. P a g e | 4 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g end xnor_gate; architecture Behavioral of xnor_gate is begin s <= p xnor q ; end Behavioral; RTL schematics : INVERTER: AND GATE: OR GATE:

- 5. P a g e | 5 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g NAND GATE: NOR GATE : EX-OR GATE:

- 6. P a g e | 6 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g EX-NOR GATE: Simulation result : INVERTER : AND GATE: OR GATE :

- 7. P a g e | 7 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g NAND GATE: NOR GATE: EX-OR GATE : EX-NOR GATE :

- 8. P a g e | 8 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 2 Objective: - Implemented half adder using VHDL. (Data flow, structural and behavioral modelling.) 1. VHDL code for Half adder in dataflow Modelling. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; ---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity Half_adder is Port ( m,n : in STD_LOGIC; s : out STD_LOGIC; c : out STD_LOGIC); end Half_adder; architecture Behavioral of Half_adder is begin s<= m xor n; c<= m and n; end Behavioral;

- 9. P a g e | 9 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 2. VHDL code for structural modelling. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Half_adder _structural is port(m,n : in STD_LOGIC; s: out STD_LOGIC); end Half_adder_structural ; architecture Behavioral of Half_adder_structural is component and_gate_2IP is Port( m,n : in STD_LOGIC; S:out STD_LOGIC); end component ; component xor_gate_2IP is port (m,n : in STD_LOGIC; s:out STD_LOGIC); begin X1:xor_gate_2IP port map(m,n,s); A1:and_gate_2IP port map(m,n,c); end behavioral;

- 10. P a g e | 10 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 3. VHDL code for Half Adder in Behavioral Modelling. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC ARITH.ALL; use IEEE.STD_LOGIC 1UNSIGNED.ALL; entity Half Adder Behavioral is Port ( m,n : in STD LOGIC; s,c : out STD_LOGIC); end Half Adder_Behavioral; architecture Behavioral of Half Adder Behavioral is begin process(m,n) begin if (m/=n) then s<=' 1 ; else s<='0'; end if; end process; process(m,n) begin if ((m=’1’) and (n=’1’) then s<=’1’; else c<=’0’; end if; end process; end Behavioral ;

- 11. P a g e | 11 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : Simulation Result :

- 12. P a g e | 12 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 3 Objective: - Implanted the Full adder using VHDL(Data flow, Structural and behavioural modelling.) 1. DATA FLOW library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity FA is Port ( X : in STD_LOGIC; Y : in STD_LOGIC; Z : in STD_LOGIC; S : out STD_LOGIC; C : out STD_LOGIC); end FA; architecture Behavioral of FA is begin S <= X XOR Y XOR Z; C <= (X AND Y) OR (Y AND Z) OR (Z AND X); end Behavioral;

- 13. P a g e | 13 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : Simulation result :

- 14. P a g e | 14 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 4 Objective: - Implanted the Half subtractor And Full subtractor. 1. HALF SUBSTRACTOR in DATA FLOW library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity HALF_SUB_STRUCT is Port ( V,R : in STD_LOGIC; S : out STD_LOGIC; B : out STD_LOGIC); end HALF_SUB; architecture Behavioral of HALF_SUB is begin S <= V xor R; B <= ((not V) and R); end Behavioral; 2. HALF SUBTRACTOR IN STRUCTURAL MODELLING library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

- 15. P a g e | 15 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g entity HALF_SUB_STRUCT is Port ( V,R : in STD_LOGIC; S : out STD_LOGIC; B : out STD_LOGIC); end HALF_SUB; architecture Behavioral of HALF_SUB is component and_gate_2IP is Port(j,k : in STD_LOGIC; l : out STD_LOGIC); end component; Component Xor_gate_2IP is Port(j,k : in SYD_LOGIC; l : out STD_LOGIC); begin S : Xor_gate_2IP port map (j,k,l); V : and_gate_2IP port map ((not j),k,l,l0); end Behavioral; 2.1 FULL SUBSTRATOR library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity FS is Port ( X : in STD_LOGIC; Y : in STD_LOGIC; Z : in STD_LOGIC; D : out STD_LOGIC; B : out STD_LOGIC); end FS; architecture Behavioral of FS is begin D <= X XOR Y XOR Z; B <= ((NOT X)AND Y)OR(Y AND Z)OR((NOT X) AND Z); end Behavioral;

- 16. P a g e | 16 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : HALF SUBSTRATOR RTl Schematics in data flow FULL SUBSTRATOR RTL Schematics in data flow

- 17. P a g e | 17 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics in Structural modelling Simulation Result : HALF SUBSTRATOR : FULL SUBSTRATOR :

- 18. P a g e | 18 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 5 Objective: - TO Design a Full adder Using Half Adder. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity full_half_adder is Port ( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; sum_fa : out STD_LOGIC; carry_fa : out STD_LOGIC); end full_half_adder; architecture structure of full_half_adder is component half_adder is port(a,b :in STD_LOGIC; sum,carry :out STD_LOGIC); end component half_adder; component or_gate is port(a,b:in STD_LOGIC; c:out STD_LOGIC);

- 19. P a g e | 19 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g end component or_gate; signal s1,c1,c2: STD_LOGIC; begin X1 : half_adder port map (a, b, s1, c1); X2 : half_adder port map(s1, c, sum_fa, c2); X3 : or_gate port map(c1, c2, carry_fa); end structure; RTL Schematics : Simulation Result :

- 20. P a g e | 20 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: _________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 6 Objective: - To design the RIPPLE CARRY ADDER using VHDL. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ripple_carry is Port ( a1,a2,a3,a4 : in STD_LOGIC; b1,b2,b3,b4 : in STD_LOGIC; s1,s2,s3,s4,carry : out STD_LOGIC); end ripple_carry; architecture Behavioral of ripple_carry is component full_adder is Port ( i1,i2,i3 : in STD_LOGIC; sum : out STD_LOGIC; carry : out STD_LOGIC); end component full_adder; component half_adder is Port ( a : in STD_LOGIC; b : in STD_LOGIC; sum : out STD_LOGIC;

- 21. P a g e | 21 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g carry : out STD_LOGIC); end component half_adder; signal c1,c2,c3: STD_LOGIC; begin HA1: half_adder port map (a1,b1,s1,c1); FA2: full_adder port map (a2,b2,c1,s2,c2); FA3: full_adder port map (a3,b3,c2,s3,c3); FA4: full_adder port map (a4,b4,c3,s4,carry); end Behavioral; RTL Schematics:

- 22. P a g e | 22 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics for Ripple carry adder Simulation result :

- 23. P a g e | 23 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2016-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 7 Objective: - Implement 2x4 and 3x8 Decoders using VHDL (Structural, Dataflow & Behavioral modelling). 1. 2X4 DECODER in Data flow . library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity decoder_2X4 is Port ( i : in STD_LOGIC_VECTOR (1 downto 0); y : out STD_LOGIC_VECTOR (3 downto 0)); end decoder_2X4; architecture Behavioral of decoder_2X4 is begin process(i) begin if i="00" then y<="0001"; elsif i="01" then y<="0010"; elsif i="10" then y<="0100"; elsif i="11" then y<="1000"; else y<="0000"; end if; end process; end Behavioral;

- 24. P a g e | 24 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 2. 2X4 DECODER in Behavioral modelling library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity decoder_2X4_dfm is Port ( x,y : in STD_LOGIC; z : out STD_LOGIC_VECTOR (3 downto 0)); end decoder_2X4_dfm; architecture Behavioral of decoder_2X4_dfm is signal not_x,not_y : STD_LOGIC; begin not_x<= not(x); not_y<= not(y); z(0)<= not_x and not_y; z(1)<= not_x and y; z(2)<= x and not_y; z(3)<= x and y; end Behavioral; 3. 2X4 DECODER in Structural Modelling library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity decoder_2X4_sm is Port ( x,y : in STD_LOGIC; z0,z1,z2,z3 : out STD_LOGIC); end decoder_2X4_sm; architecture Behavioral of decoder_2X4_sm is component not_gate is

- 25. P a g e | 25 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g port(x :in STD_LOGIC; y :out STD_LOGIC); end component not_gate; component and_gate is port(x,y:in STD_LOGIC; z:out STD_LOGIC); end component and_gate; signal not_x,not_y: STD_LOGIC; begin X1 : not_gate port map (x,not_x); X2 : not_gate port map (y,not_y); X3 : and_gate port map (not_x,not_y,z0); X4 : and_gate port map (not_x,y,z1); X5 : and_gate port map (x,not_y,z2); X6 : and_gate port map (x,y,z3); end Behavioral; RTL Schematics : RTL Schematics in DATA FLOW

- 26. P a g e | 26 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics in Behavioral modelling. RTL Schematics in Structural modelling. Simulation Result :

- 27. P a g e | 27 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 1.1 3X8 DECODER in DATA FLOW : library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity decoder_3X8_df is Port ( i : in STD_LOGIC_VECTOR (2 downto 0); Y : out STD_LOGIC_VECTOR (7 downto 0)); end decoder_3X8_df; architecture Behavioral of decoder_3X8_df is begin Y(0)<= not(i(2))and not(i(1)) and not(i(0)) ; Y(1)<= not(i(2))and not(i(1)) and i(0) ; Y(2)<= not(i(2))and i(1) and not(i(0)) ; Y(3)<= not(i(2))and i(1) and i(0) ; Y(4)<= i(2)and not(i(1)) and not(i(0)) ; Y(5)<= i(2)and not(i(1)) and i(0) ; Y(6)<= i(2)and i(1) and not(i(0)) ; Y(7)<= i(2)and i(1) and i(0) ; end Behavioral; 1.2 3X8 DECODER IN STRUCTURAL MODELLING library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity DEC_3X8_BEHAvior is Port (w,x,y,z ,Ein: in STD_LOGIC; v: out STD_LOGIC_VECTOR (7 downto 0); end DEC_3X8_BEHAvior; architecture Behavioral of DEC_3X8_BEHAvior is component And_gate_4IP is port (p,q,r,s : in STD_LOGIC; t :out STD_LOGIC); end component; begin V1: And_gate_4IP port map((not y),(not x),(not w),Ein,v(0)); V2: And_gate_4IP port map((not y),(not x),w,Ein,v(1)); V3 : And_gate_4IP port map((not y),x,(not w),Ein,v(2)); V4 : And_gate_4IP port map((not y),x,w,Ein,v(3)); V5 : And_gate_4IP port map (y,(not x),(not w),Ein,(v4)); V6 : And_gate_4IP port map (y,(not x),w,Ein,v(5));

- 28. P a g e | 28 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g V7 : And_gate_4IP port map (y,x,(not w),Ein,v(6)); V8 : And_gate_4IP port map (y,x,w,Ein,v(7)); end Behavioral; 1.3 3X8 IN BEHAVIORAL MODELLING : USING WHEN_ELSE STATEMENT library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity DCE_3x8_WHEN_ELSE is Port ( L : in STD_LOGIC_VECTOR (2 downto 0); I : in STD_LOGIC; O : out STD_LOGIC_VECTOR (7 downto 0)); end DCE_3x8_WHEN_ELSE; architecture Behavioral of DCE_3x8_WHEN_ELSE is signal VEE : STD_LOGIC_VECTOR(3 downto 0); begin VEE <= I & L; O<= "00000001" when (VEE="1000")else "00000010" when (VEE="1001")else "00000100" when (VEE="1010")else "00001000" when (VEE="1011")else "00010000" when (VEE="1100")else "00100000" when (VEE="1101")else "01000000" when (VEE="1110")else "10000000" when (VEE="1111")else "00000000"; end Behavioral;

- 29. P a g e | 29 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : Simulation Result :

- 30. P a g e | 30 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 201-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 8 Objective: - Implement 8X3 ENCODER using VHDL (Structural, Dataflow & Behavioral modelling). 1. 8X3 ENCODER in Data flow . library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity encoder_8X3 is Port ( i : in STD_LOGIC_VECTOR (7 downto 0); L : out STD_LOGIC_VECTOR (2 downto 0)); end encoder_8X3; architecture Behavioral of encoder_8X3 is begin L(0)<= K(1) or K(3) or K(5) or K(7); L(1)<= K(2) or K(3) or K(6) or K(7); L(2)<= K(4) or K(5) or K(6) or K(7); end Behavioral; 2. 8X3 ENCODER IN BEHAVIORAL MODELLING library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity encoder_8X3_bm is Port ( K : in STD_LOGIC_VECTOR (7 downto 0); L : out STD_LOGIC_VECTOR (2 downto 0)); end encoder_8X3_bm; architecture Behavioral of encoder_8X3_bm is signal a1,a2,b1,b2,c1,c2: STD_LOGIC; begin a1<= K(1) or K(3); a2<= K(5) or K(7); b1<= K(2) or K(3); b2<= K(6) or K(7); c1<= K(4) or K(5);

- 31. P a g e | 31 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g c2<= K(6) or K(7); L(0)<= a1 or a2; L(1)<= b1 or b2; L(2)<= c1 or c2; end Behavioral; 3. USE WHEN_ELESE STATEMENT 4. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ENCOD_8x3_WhenElse is Port ( P : in STD_LOGIC_VECTOR (7 downto 0); Ein : in STD_LOGIC; K : out STD_LOGIC_VECTOR (2 downto 0)); end ENCOD_8x3_WhenElse; architecture Behavioral of ENCOD_8x3_WhenElse is signal Iin : STD_LOGIC_VECTOR(8 downto 0); begin Iin <= Ein & P; K <= "000" when(Iin="100000001")else "001" when(Iin="100000010")else "010" when(Iin="100000100")else "011" when(Iin="100001000")else "100" when(Iin="100010000")else "101" when(Iin="100100000")else "110" when(Iin="101000000")else "111" when(Iin="110000000")else "000"; end Behavioral;

- 32. P a g e | 32 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : RTL Schematics in data flow RTL Schematics in Behavioral modelling Simulation result :

- 33. P a g e | 33 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: __________________________________ Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO.9 Objective: - Implementation the 4X1 Multiplexer using VHDL code (Data flow , Behavioral and structural modelling.) 1. VHDL code for 4x1 Mux in Data Flow Modelling. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity MUX_4X1 is Port ( I : in STD_LOGIC_VECTOR (3 downto 0); X: in STD_LOGIC_VECTOR (1 downto 0); Y : out STD_LOGIC); end MUX_4X1; architecture Behavioral of MUX_4X1 is signal temp1,temp2:STD_LOGIC; begin temp1<=not X(1); temp2<=not X(0); Y <= (( temp(1) and temp(2) and I(0)) or (( temp(1)and X(2) and I(1)) or ((X(1) and temp(2) and I(2)) or ((X(1) and X(2) and I(3)); end Behavioral;

- 34. P a g e | 34 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 2. VHDL code for 4x1 Mux in Behavioral Modelling. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity MUX_4X1 is Port ( I : in STD_LOGIC_VECTOR (3 downto 0); X: in STD_LOGIC_VECTOR (1 downto 0); Y : out STD_LOGIC); end MUX_4X1; architecture Behavioral of MUX_4X1 is begin process(I,X) begin if X="00" then Y <=I(0); elsif X="01" then Y<=I(1); elsif X="10" then Y<=I(2); elsif X="11" then Y<=I(3); end if; end process; end Behavioral;

- 35. P a g e | 35 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g 3. VHDL code for 4x1 Mux in structural Modelling. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity MUX_4X1 is Port ( I : in STD_LOGIC_VECTOR (3 downto 0); X: in STD_LOGIC_VECTOR (1 downto 0); Y : out STD_LOGIC); end MUX_4X1; architecture Behavioral of MUX_4X1 is Component and_gate_3IP is Port (p,q,r, :in STD_LOGIC; s : out STD_LOGIC); end component; Component and_gate_4IP is Port (p,q,r,s :in STD_LOGIC; t: out STD_LOGIC); end component; signal temp1,temp2,temp3,temp4 :STD_LOGIC; begin A1: and_gate_3IP port map((not X(1),not X(0),I(0),temp1); A2: and_gate_3IP port map((not X(1), X(0),I(1),temp2); A3: and_gate_3IP port map((X(1),not X(0),I(2),temp3); A4: and_gate_3IP port map(( X(1),not X(0),I(3),temp4); Y1 :Or_gate_4IP port map(temp1,temp2,temp3,temp4,Y); end Behavioral;

- 36. P a g e | 36 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : RTL Schematics in Behavioral modelling. RTL Schematics in Data flow. RTL Schematics in Structural modelling. Simulation Result :

- 37. P a g e | 37 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 10 Objective: - Implemented the 2 bit binary comparator by VHDL. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity comp_2bit is Port ( A,B : in STD_LOGIC_VECTOR (1 downto 0); X,Y,Z : out STD_LOGIC); end comp_2bit; architecture Behavioral of comp_2bit is begin process (A, B) variable X_tmp : std_logic; variable Y_tmp : std_logic; variable Z_tmp : std_logic; begin -- process X_tmp := '0'; Y_tmp := '0'; Z_tmp := '0'; If A > B then X_tmp := '1'; elsif A = B then Y_tmp := '1'; else Z_tmp := '1'; end if; X <= X_tmp; Y <= Y_tmp;

- 38. P a g e | 38 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g Z <= Z_tmp; end process; end Behavioral; RTL schematics : RTL Schematics Simulation result :

- 39. P a g e | 39 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 11 Objective: - Implemented 4X2 Encoder Using VHDL. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity encoder_case is port( din : in STD_LOGIC_VECTOR(3 downto 0); dout : out STD_LOGIC_VECTOR(1 downto 0); end encoder_case; architecture encoder_case_arc of encoder_case is begin encoder : process (din) is begin case din is when "1000" => dout <= "00"; when "0100" => dout <= "01"; when "0010" => dout <= "10"; when "0001" => dout <= "11"; when others => dout <= "ZZ"; end case; end process encoder; end encoder_case_arc; end Behavioral;

- 40. P a g e | 40 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : Simulation Result :

- 41. P a g e | 41 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 12 Objective: - Implemented Binary to Gray converter. library IEEE; use IEEE.STD_LOGIC_1164.all; entity binary_to_gray is port( din : in STD_LOGIC_VECTOR(3 downto 0); dout : out STD_LOGIC_VECTOR(3 downto 0); end binary_to_gray; architecture binary_to_gray_arc of binary_to_gray is begin dout(3) <= din(3); dout(2) <= din(3) xor din(2); dout(1) <= din(2) xor din(1); dout(0) <= din(1) xor din(0); end binary_to_gray_arc; end Behavioral;

- 42. P a g e | 42 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics: RTL Schematics of Binary to gray converter. Simulation result:

- 43. P a g e | 43 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO.13 Objective: - Implemented to GRAY to BINARY code converter using VHDL. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Gray_to_binary is Port ( G : in STD_LOGIC_VECTOR (3 downto 0); B : out STD_LOGIC_VECTOR (3 downto 0)); end Gray_to_binary; architecture Behavioral of Gray_to_binary is begin process (G) begin if G="0000" then B<="0000"; elsif G="0001" then B<="0001"; elsif G="0010" then B<="0011"; elsif G="0100" then B<="0110"; elsif G="0101" then B<="0111"; elsif G="0110" then B<="0101"; elsif G="0111" then B<="0100"; elsif G="1000" then B<="1100"; elsif G="1001" then B<="1101"; elsif G="1010" then B<="1111";

- 44. P a g e | 44 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g elsif G="1011" then B<="1110"; elsif G="1100" then B<="1010"; elsif G="1101" then B<="1011"; elsif G="1110" then B<="1001"; elsif G="1111" then B<="1000"; end if; end process; end Behavioral; RTL Schematics : Simulation Result :

- 45. P a g e | 45 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 14 Objective: - Implemented BCD code to SEVEN SEGMENT Display code using VHDL. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Bcd_7seg is Port ( clk : in STD_LOGIC; bcd : in STD_LOGIC_VECTOR(3 downto 0); segment7 : out STD_LOGIC_VECTOR(7 downto 0); end Bcd_7seg; architecture Behavioral of Bcd_7seg is begin process (clk,bcd)is begin if (clk'event and clk='1') then case bcd is when "0000"=> segment7 <="0000001"; when "0001"=> segment7 <="1001111"; when "0010"=> segment7 <="0010010"; when "0011"=> segment7 <="0000110"; when "0100"=> segment7 <="1001100"; when "0101"=> segment7 <="0100100"; when "0110"=> segment7 <="0100000"; when "0111"=> segment7 <="0001111"; when "1000"=> segment7 <="0000000"; when "1001"=> segment7 <="0000100"; when others=> segment7 <="1111111";

- 46. P a g e | 46 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g end case; end if; end process; end Behavioral; RTL Schematics : Simulation Result :

- 47. P a g e | 47 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKY Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 15 Objective: Implemented the BCD to EXCESS-3 Code converter. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity BCD_XS3 is port( A, B, C, D : in std_logic; W, X, Y, Z : out std_logic); end BCD_XS3; architecture BCD_Func of BCD_XS3 is component andGate is port( A, B : in std_logic; F : out std_logic); end component; component orGate is port( A, B : in std_logic; F : out std_logic); end component; component xorGate is port( A, B : in std_logic; F : out std_logic); end component; component notGate is port( inPort : in std_logic; outPort : out std_logic); end component; signal andOut, orOut, xorOut: std_logic;

- 48. P a g e | 48 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g begin G1: orGate port map(A, andOut, W); G2: andGate port map(B, orOut, andOut); G3: orGate port map(C, D, orOut); G4: xorGate port map(orOut, B, X); G5: xorGate port map(C, D, xorOut); G6: notGate port map(xorOut, Y); G7: notGate port map(D, Z); end BCD_Func; ` end Behavioral; RTL Schematics : Simulation result :

- 49. P a g e | 49 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: __________________________________ Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO.16 Objective: - Implementation the various flip flop. DELAY F/F : library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity delay_flip_flop is Port ( RST,CLK : in STD_LOGIC; Jin : in STD_LOGIC; Qout : out STD_LOGIC); end delay_flip_flop; architecture Behavioral of delay_flip_flop is begin process(Jin,CLK) begin if(CLK='1' and CLK'event) then Qout <=Jin; if(RST='1') then Qout<='0'; else Qout<=Jin; end if; end if; end process; J-K F/F :

- 50. P a g e | 50 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity JK_Flipflop is port ( clk: in std_logic; J, K: in std_logic; Q, Qbar: out std_logic; reset: in std_logic); end JK_Flipflop; architecture Behavioral of JK_Flipflop signal qtemp,qbartemp : std_logic :='0'; begin Q <= qtemp; Qbar <= qbartemp; process(clk,reset) begin if(reset = '1') then qtemp <= '0'; qbartemp <= '1'; elsif( rising_edge(clk) ) then if(J='0' and K='0') then NULL; elsif(J='0' and K='1') then qtemp <= '0'; qbartemp <= '1'; elsif(J='1' and K='0') then qtemp <= '1'; qbartemp <= '0'; else qtemp <= not qtemp; qbartemp <= not qbartemp; end if; end if; end process; end Behavioral;

- 51. P a g e | 51 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g TOGGLE_F/F library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity TOGGLE_FF is Port( T,CLK,PRESET,SET : in STD_LOGIC; Q,Qnot : out STD_LOGIC); End TOGGLE_FF; architecture Behavioral of TOGGLE_FF is begin process (CLK,PRESET,SET) variable X : STD_LOGIC; begin if(SET ='0') then X :='0'; elsif (SET='1' and PRESET='0')then X:='1'; elsif(CLK='1' and CLK'event) then if (T='1')then X :=not X; end if; end if; Q<=X; Qnot <= not X; end process; end Behavioral; RTL Schematics : DELAY F/F :

- 52. P a g e | 52 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics of Delay flip flop J_K_FLIP_FLOP RTL Schematics of JK_Flip flop TOGGLE F/F : RTL Schematics of Toggle flip flop

- 53. P a g e | 53 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g Simulation Result : DELAY F/F JK_F/F TOGGLE F/F

- 54. P a g e | 54 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: __________________________________ Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 17 Objective: Implemented the MOD 16 UP counter. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity bit4_up is Port ( count : out STD_LOGIC_VECTOR (3 downto 0); clk : in STD_LOGIC); end bit4_up; architecture Behavioral of bit4_up is signal cnt:STD_LOGIC_VECTOR (3 downto 0) := "1111" ; begin process (clk) begin if ( clk = '1') AND( clk'LAST_VALUE = '0') then count <= cnt+1; cnt <= cnt+1; end if; end process; end Behavioral;

- 55. P a g e | 55 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : Simulation Result :

- 56. P a g e | 56 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: __________________________________ Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO.18 Objective: - Design of counter MOD-16 up-down counter. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity MOD_16_up_down_counter is Port ( CLK : in STD_LOGIC; RST : in STD_LOGIC; DTN : in STD_LOGIC; OUTP : out STD_LOGIC_VECTOR (0 downto 3)); end MOD_16_up_down_counter; architecture Behavioral of MOD_16_up_down_counter is signal temp : STD_LOGIC_VECTOR(0 to 3); begin process(CLK,RST) begin if RST='1' then temp<="0000"; elsif(CLK'event and CLK='1') then if(DTN='0') then temp<=temp+ '1'; elsif(DTN='1') then temp<=temp- '1'; end if; end if; end process; end Behavioral;

- 57. P a g e | 57 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : RTL schematics for MOD-16 bit up down counter Simulation result :

- 58. P a g e | 58 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: __________________________________ Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO.19 Objective: - Implemented design of synchronous 8 Bit Jhonson Counter. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Jhonson_counter_8bit is Port ( CLK : in STD_LOGIC; RST : in STD_LOGIC; O : out unsigned (3 downto 0)); end Jhonson_counter_8bit; architecture Behavioral of Jhonson_counter_8bit is signal temp : unsigned(3 downto 0):=(others=>'0'); begin O<=temp; process(CLK) begin if (rising_edge(CLK))then if (RST='1') then temp <=(others=>'0'); else temp(1) <=temp(0); temp(2) <=temp(1); temp(3) <=temp(2); temp(0) <=not temp(3); end if; end if; end process; end Behavioral;

- 59. P a g e | 59 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g RTL Schematics : RTL Schematics of 8 Bit Jhonson Counter Simulation result :

- 60. P a g e | 60 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g SHRI G. S. INSTITUTE OF TECHNOLOGY AND SCIENCE DEPARTMENT OF ELECTRONICS AND INSTRUMENTATION ENGINEERING Subject: VLSI Design Subject code: EI 4755 Name of Student: VEER SINGH SHAKYA Enroll No: 0801EI121058 Session: 2015-2016 Date: __________________________ Remarks, if any: ____________________________ Signature of Lecturer VHDL CODE NO. 20 Objective: - Implemented the 4 bit Ring Counter. library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Ring_counter is Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; output : out STD_LOGIC_VECTOR (3 downto 0)); end Ring_counter; architecture Behavioral of Ring_counter is signal temp : STD_LOGIC_VECTOR(3 downto 0):=(others => '0'); begin process(clk) begin if( clk'event and clk='1' ) then if (reset = '1') then temp <= (0=> '1', others => '0'); else temp(1) <= temp(0); temp(2) <= temp(1); temp(3) <= temp(2);

- 61. P a g e | 61 D e p a r t m e n t o f E l e c t r o n i c s a n d I n s t r u m e n t a t i o n E n g i n e e r i n g temp(0) <= temp(3); end if; end if; end process; output<=temp; end Behavioral; RTL Schematics : Simulation Result :