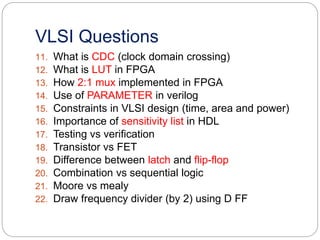

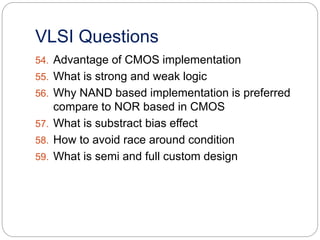

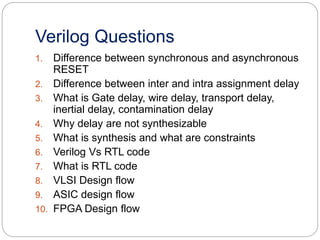

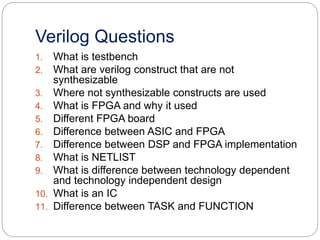

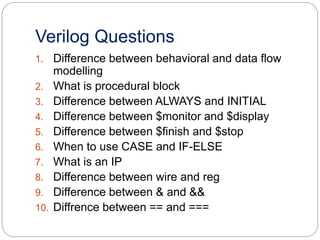

This document contains a list of interview questions related to VLSI design and Verilog. There are 77 questions related to VLSI topics such as setup and hold time, race conditions, critical paths, FPGA vs ASIC, clock domain crossing, LUTs, mux implementation, constraints, sensitivity lists, testing vs verification, latches vs flip-flops, logic types, frequency division, flip-flop designs, counter designs, number representations, hazard avoidance, CMOS basics, propagation delay, static and dynamic hazards, logic design from state diagrams, and more. It also contains 47 questions related to Verilog topics such as synchronous vs asynchronous reset, modeling styles, procedural blocks, monitoring tasks, default values, generate