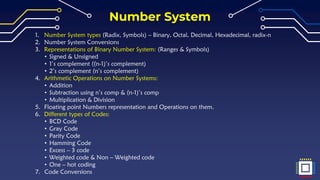

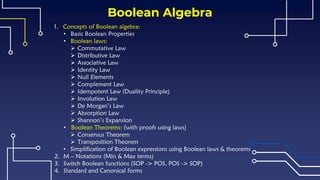

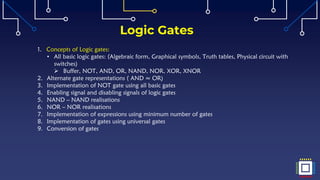

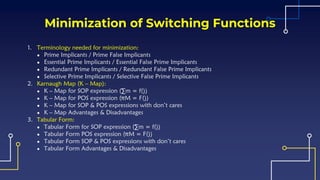

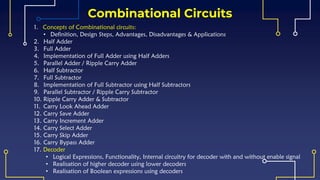

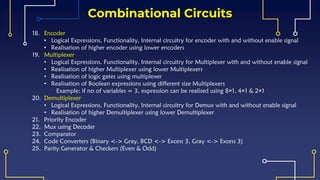

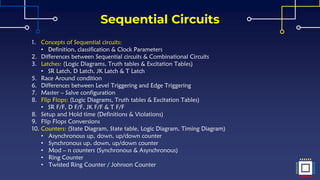

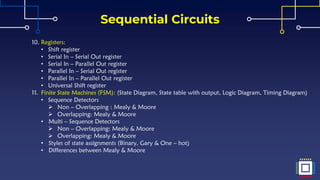

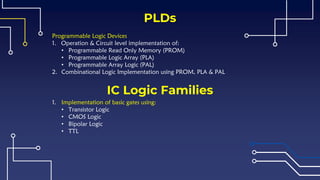

The document provides an extensive overview of digital electronics, covering key topics such as number systems, boolean algebra, logic gates, combinational and sequential circuits, and programmable logic devices. It includes detailed information on representations, operations, and design principles in digital circuits, emphasizing both theoretical concepts and practical implementations. Additionally, various coding systems, minimization techniques, and applications of digital circuits are discussed.