This document discusses system organization and input/output device interfaces. It covers several topics:

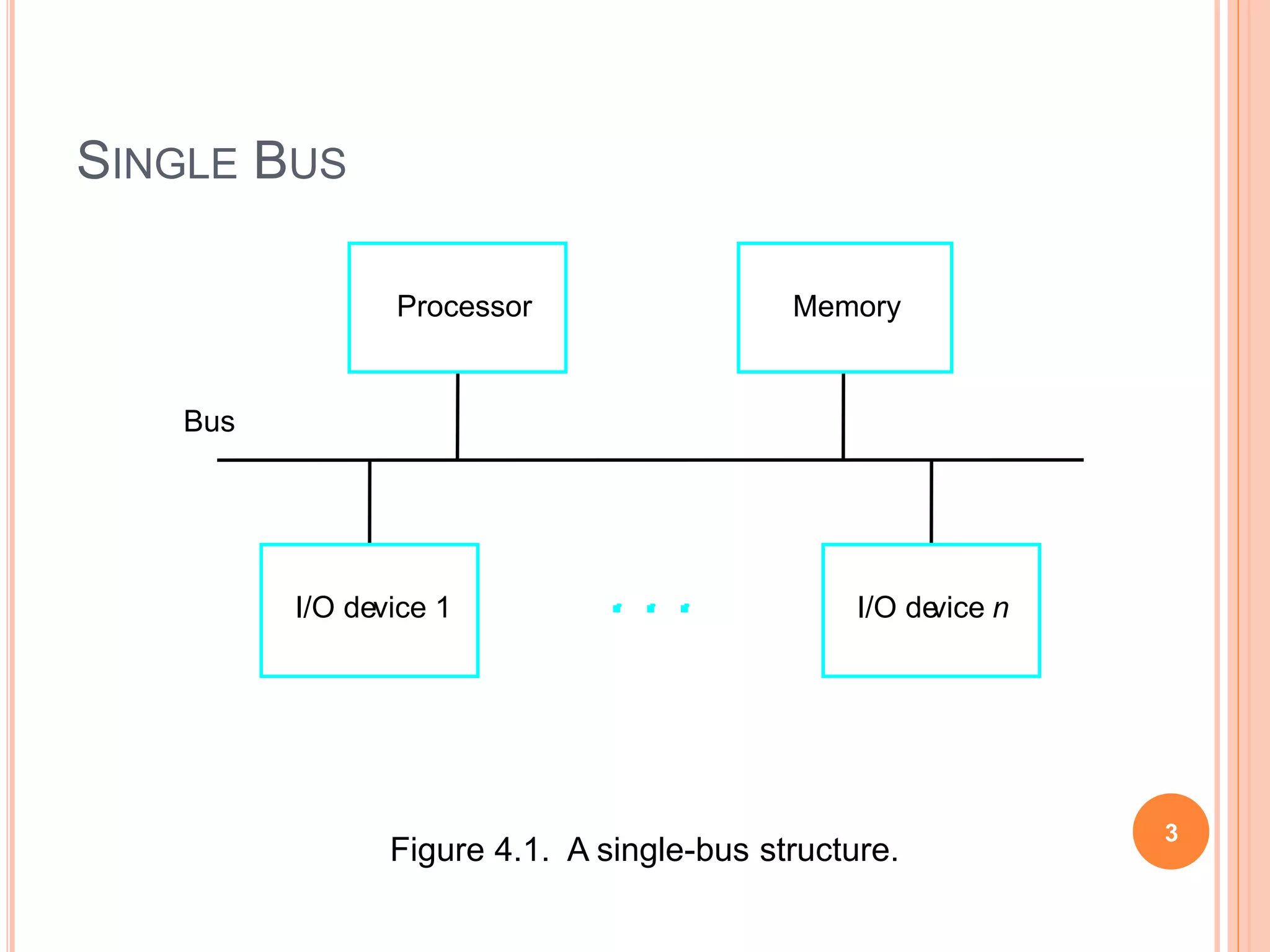

1. Single bus architecture with memory-mapped I/O and interface circuits to connect devices to the bus.

2. Program-controlled I/O using polling and interrupts to handle asynchronous devices.

3. Direct memory access (DMA) for high-speed transfer of blocks of data between memory and I/O devices.

4. Details of interrupt handling including priorities, nesting, and vectored interrupts.