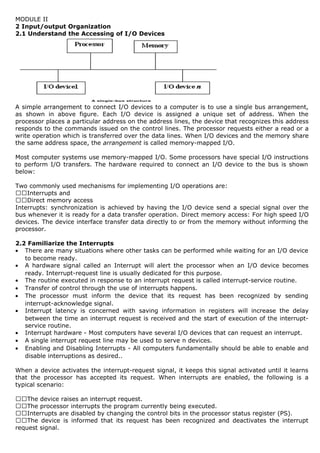

This document provides information on input/output organization and interfaces in a computer system. It discusses different I/O techniques like interrupts and direct memory access. Interrupts allow I/O devices to signal the processor when they need attention. Direct memory access enables high-speed transfer of data directly between I/O devices and memory without processor involvement. The document also describes common I/O bus standards like PCI, SCSI and USB and how they facilitate communication between devices and the computer.