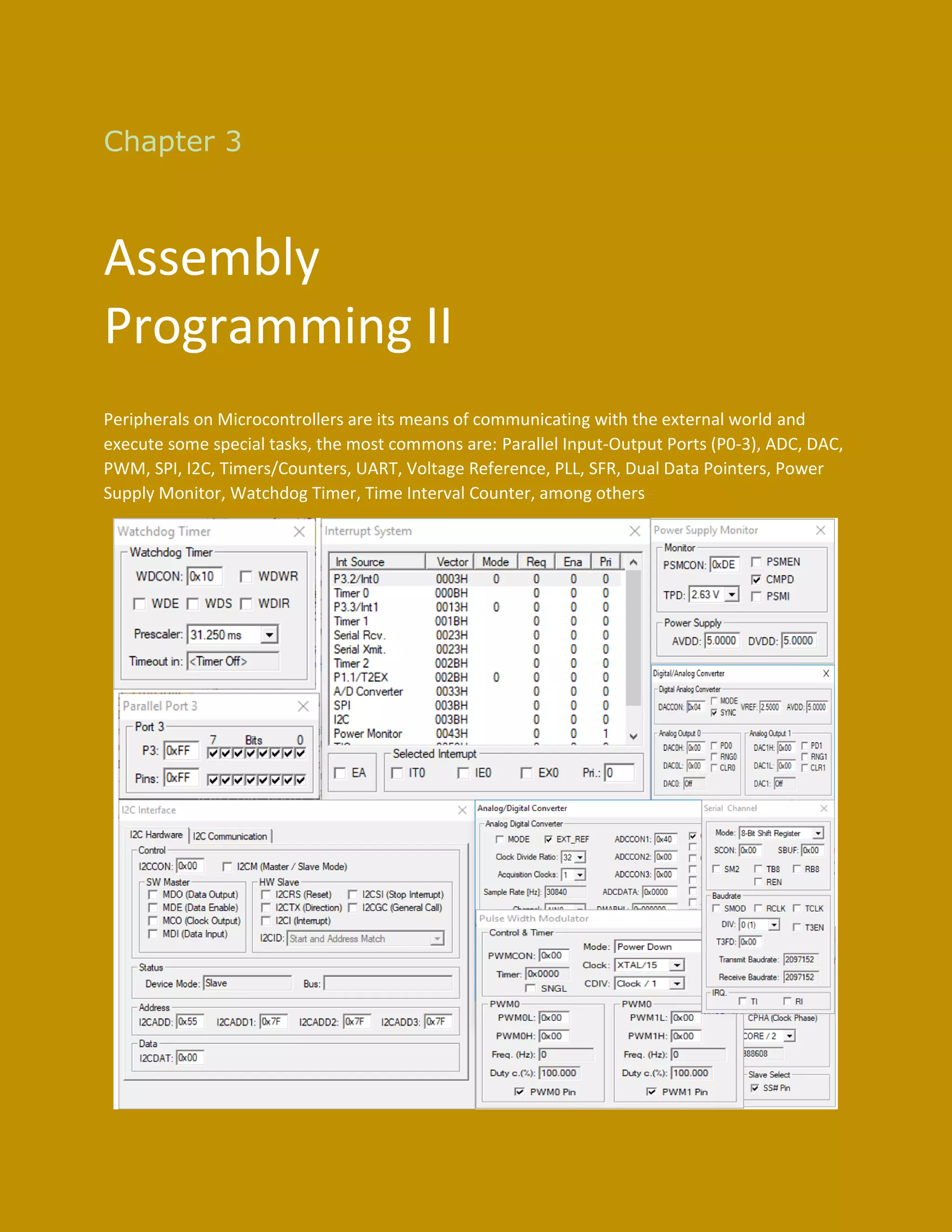

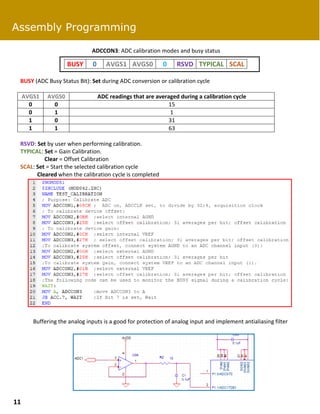

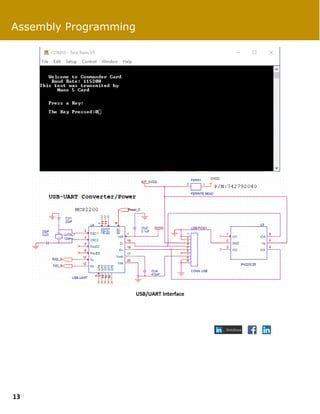

The document discusses various peripherals on microcontrollers including parallel I/O ports (P0-3), timers/counters, DAC, ADC, PWM, UART. It provides details on how each peripheral works, the registers used to control them, and examples of using timers/counters and DAC to generate waveforms.