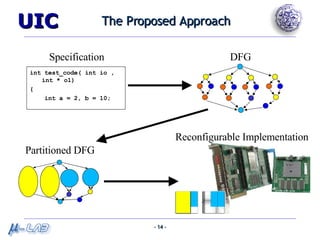

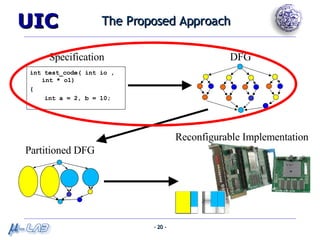

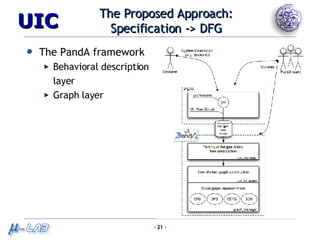

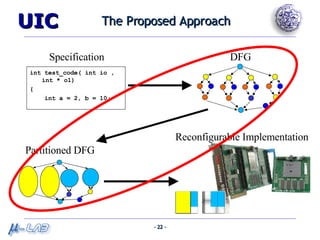

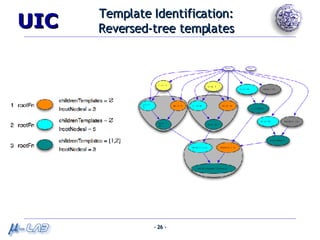

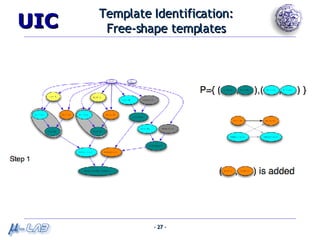

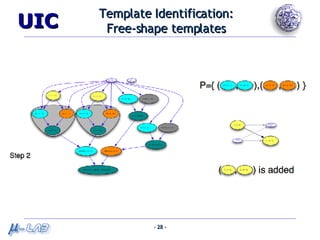

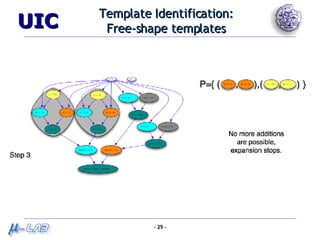

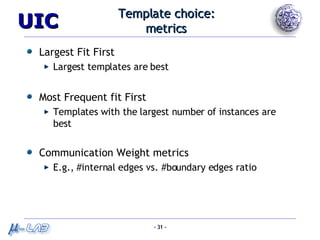

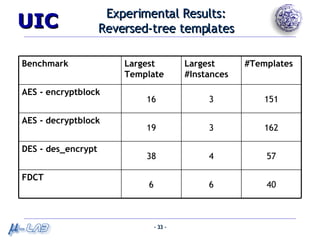

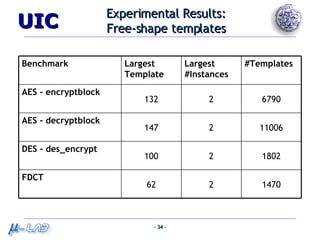

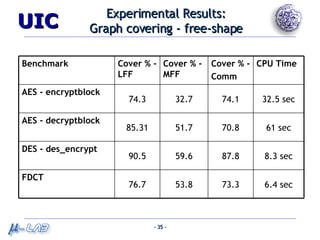

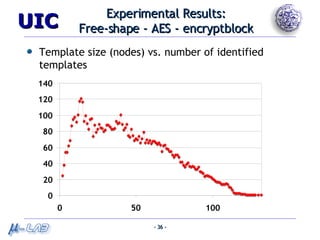

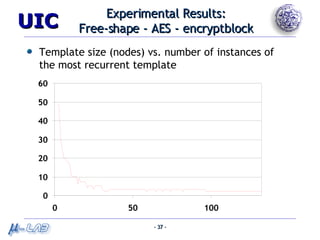

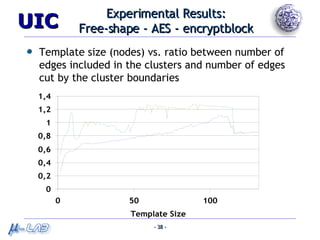

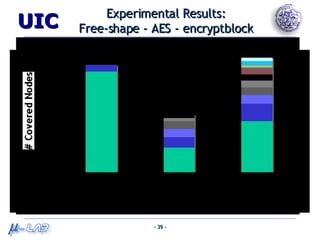

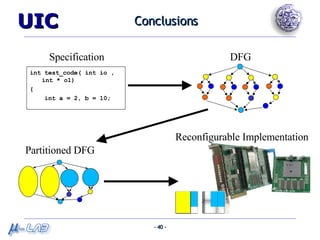

The document proposes an approach for identifying core designs for reconfigurable systems driven by specification self-similarity. It involves partitioning a specification's data flow graph (DFG) to identify recurrent subgraphs that can be implemented as reusable configurable modules. This is done through two phases: template identification to produce equivalence classes of isomorphic subgraphs, and graph covering to select templates for implementation. The approach was tested on real-world benchmarks, demonstrating coverage of 70-90% and runtimes of seconds to minutes. Future work includes refining template selection and online scheduling of reconfigurable cores.