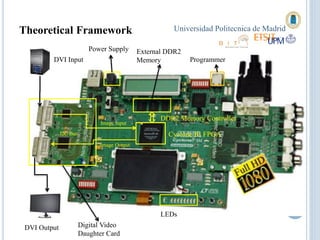

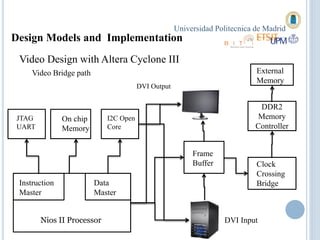

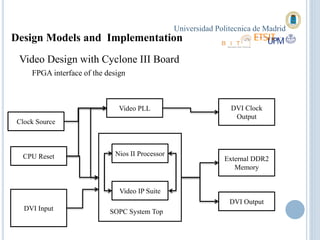

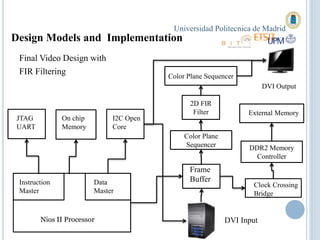

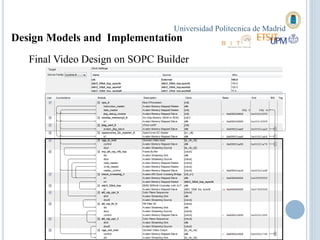

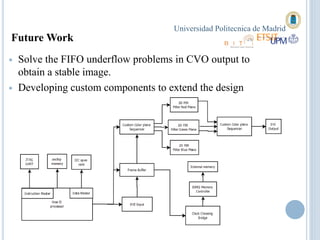

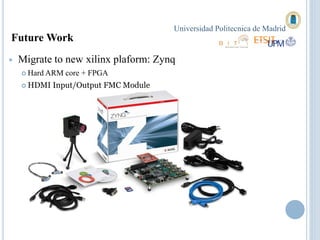

The document summarizes a master's thesis presentation on real-time image processing using an Altera FPGA. It discusses using the FPGA to process high-resolution microscope images in real-time for feedback control. It presents the problem statement, theoretical background on FPGAs and image processing, and design and implementation of a system using the Altera Cyclone III FPGA board. The design implements a Nios II soft processor, video processing IP cores, and interfaces to DDR memory and DVI input/output. Future work focuses on improving system stability and migrating to the Zynq platform.

![Universidad Politecnica de Madrid

Bibliography

Altera Corporation, "Cyclone III Device Handbook, Chapter 6: I/O Features in

the Cyclone III Device Family," 2009 December. [Online]. Available:

http://www.altera.com/literature/hb/cyc3/cyc3_ciii51007.pdf

Altera Corporation, Altera, [Online]. Available:

http://www.altera.com/devices/fpga/cyclone3/overview/architecture/cy3architect

ure.html.

Altera Corporation, "Nios II Software Developer's Handbook," May 2011.

[Online]. Available:

http://www.altera.com/literature/hb/nios2/n2sw_nii52004.pdf.

Altera Corporation, "Developing Programs Using Hardware Abstraction Layer,"

May 2011. [Online]. Available:

http://www.altera.com/literature/hb/nios2/n2sw_nii52003.pdf.

Altera Corporation, "Nios II Processor Reference Handbook," 2010 July.

[Online]. Available: http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf

Digital Display Working Group, "Digital Visual Interface DVI," 02 April 1999.

[Online]. Available: http://www.ddwg.org/lib/dvi_10.pdf

Altera Corporation, "Video and Image Processing Suite User Guide," July 2010.

[Online]. Available: http://www.altera.com/literature/an/an427.pdf

Altera Corporation, "Cyclone III 3C120 Development Board Reference Manual,“

http://www.altera.com/literature/manual/rm_cycloneiii_dev_kit_host_board.pdf](https://image.slidesharecdn.com/realtimeimageprocessinginfpga-130220110406-phpapp01/85/Real-time-image-processing-in-fpga-22-320.jpg)