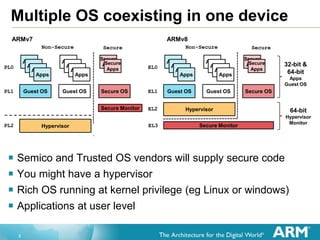

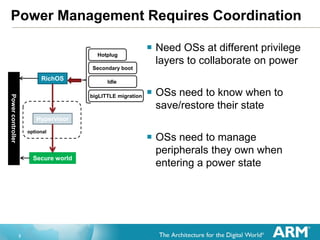

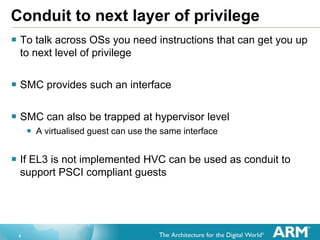

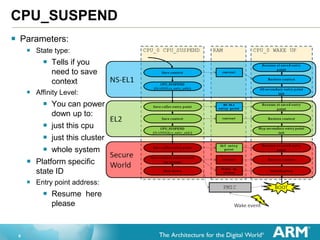

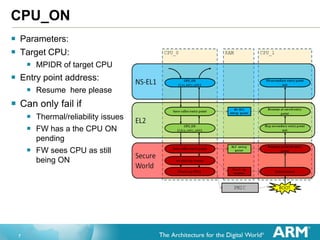

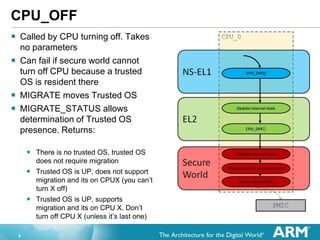

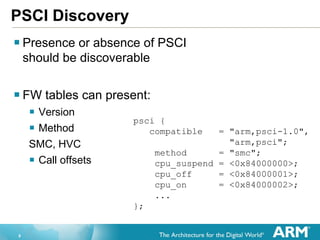

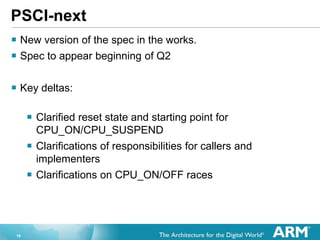

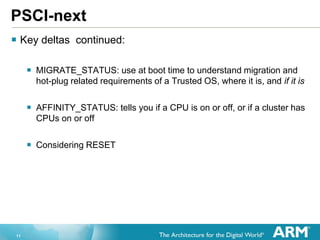

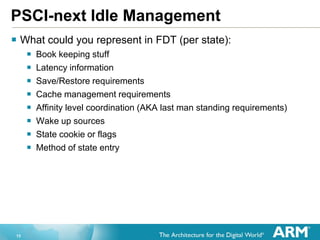

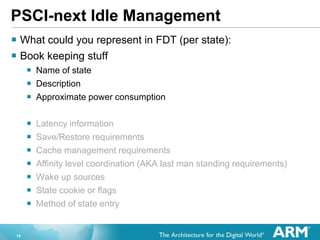

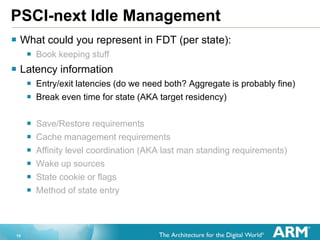

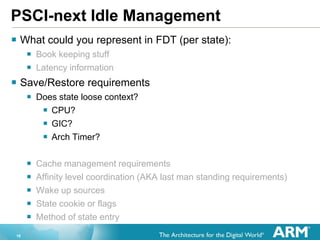

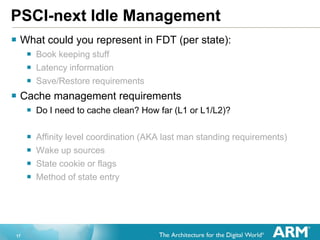

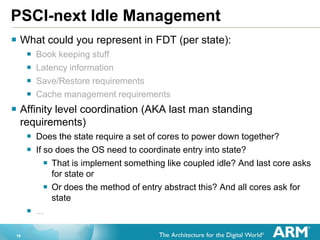

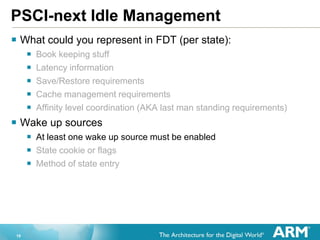

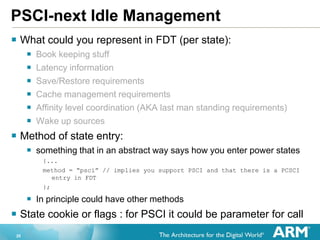

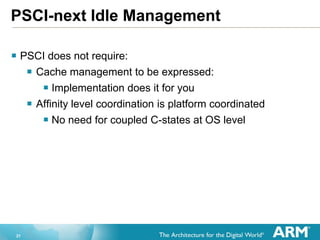

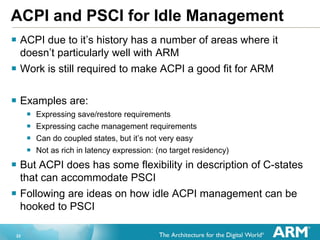

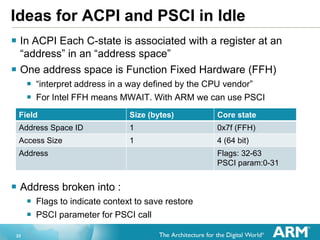

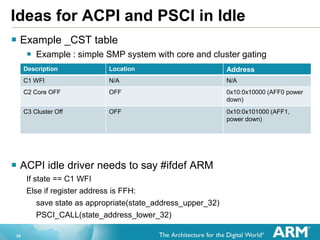

The document discusses the updates and future plans regarding the Power State Coordination Interface (PSCI) and its integration with multiple operating systems on a single device. It details the necessity for collaboration among operating systems at different privilege layers for efficient power management, highlights key APIs involved (like cpu_suspend, cpu_on, and cpu_off), and outlines the anticipated advancements in the PSCI specification. Additionally, it addresses the relationship between PSCI and ACPI, aiming to effectively adapt idle management for ARM architectures.