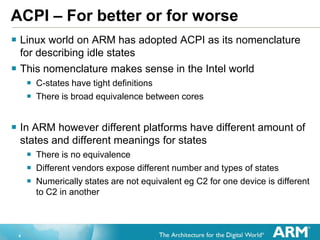

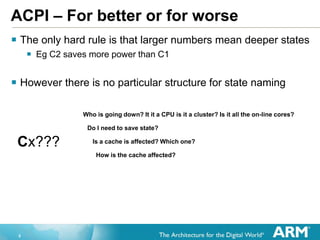

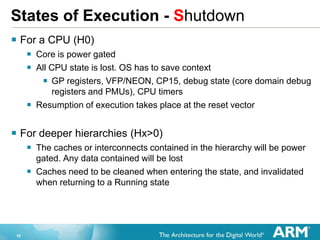

The document discusses idle power states in ARM systems, highlighting the complexity and variability across different devices and vendors. It emphasizes the need for a standardized nomenclature to facilitate comparisons and enhance OS abstraction layers, while also detailing various execution states, their implications on CPU and cache management, and the importance of latency and availability factors. The proposal outlines a hierarchical approach for power states that considers the topology of the system, aiming to improve power management strategies.

![15

State ID

Different HW platforms may support several states of each

type

It is proposed that states can have individual IDs appended to

the name of the state eg:

[R/W/S][Hierarchy level]_[StateID]](https://image.slidesharecdn.com/idlestatesnomenclatureproposal-140320104802-phpapp01/85/Q2-12-Idle-Power-States-Nomenclature-15-320.jpg)