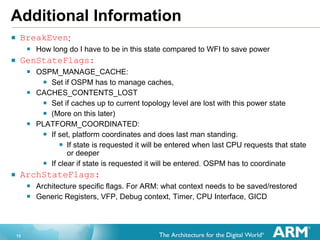

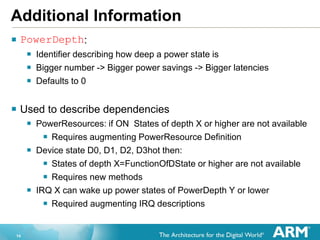

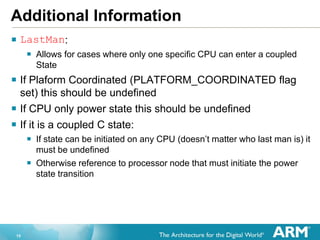

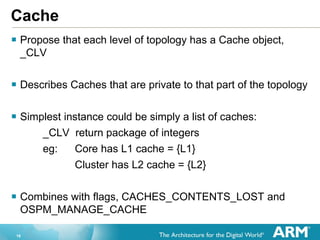

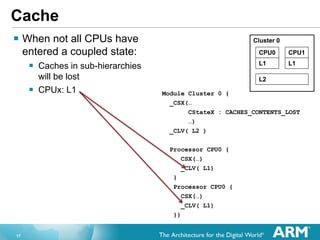

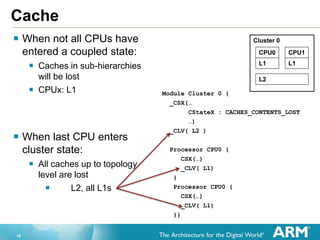

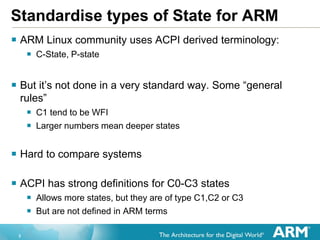

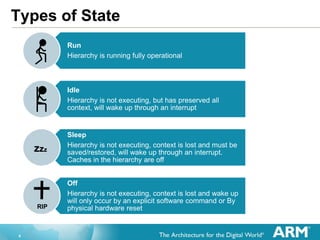

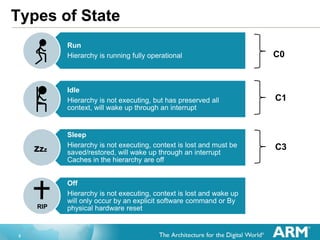

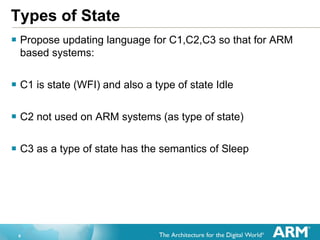

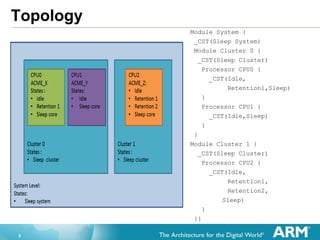

The document discusses the nuances of ACPI and its application to ARM systems, focusing on different power states (C-states) and their management. It details the inadequacies of current representations and proposes new methodologies for defining these states, emphasizing topology awareness and cache management. Suggestions include implementing a new object method (_csx) to better facilitate power state management in heterogeneous environments.

![11

Additional Information

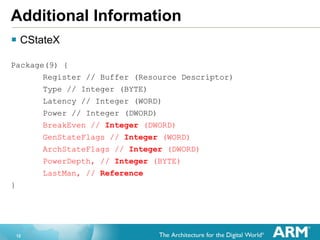

Proposal is to replace _CST with new object method _CSX

Package {

Version, // Integer (WORD)

Count, // Integer (WORD)

CStatesX[0], // Package

…

CStatesX[N-1] // Package

}

Version is self explanatory. It would start at 0](https://image.slidesharecdn.com/acpiandidlestates-140324084805-phpapp02/85/LCU13-ACPI-power-state-mapping-11-320.jpg)