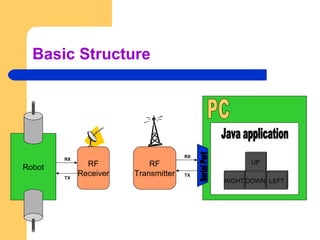

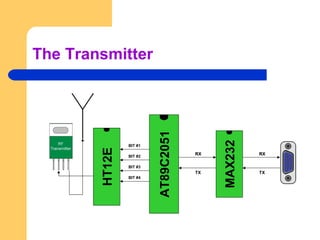

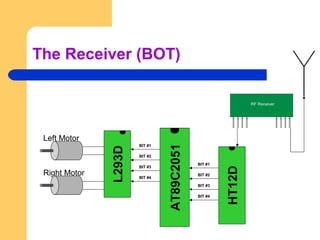

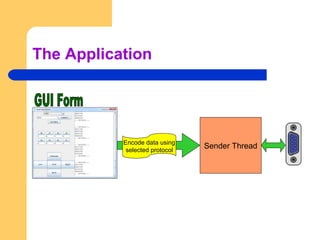

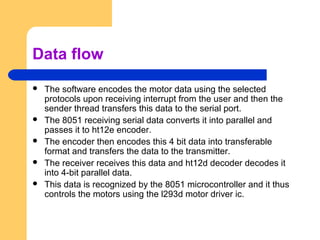

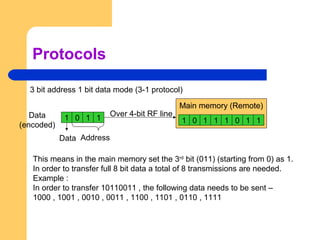

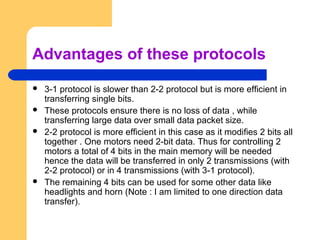

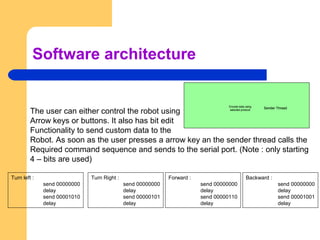

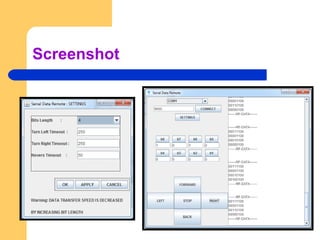

The document outlines the communication protocols and software architecture used for controlling a robot via RF transmission. It details the encoding and decoding processes involving HT12E and HT12D with different protocols for data transmission and motor control. Additionally, the software allows user interaction for controlling the robot with specified commands and includes precautions for motor control to prevent instantaneous direction changes.