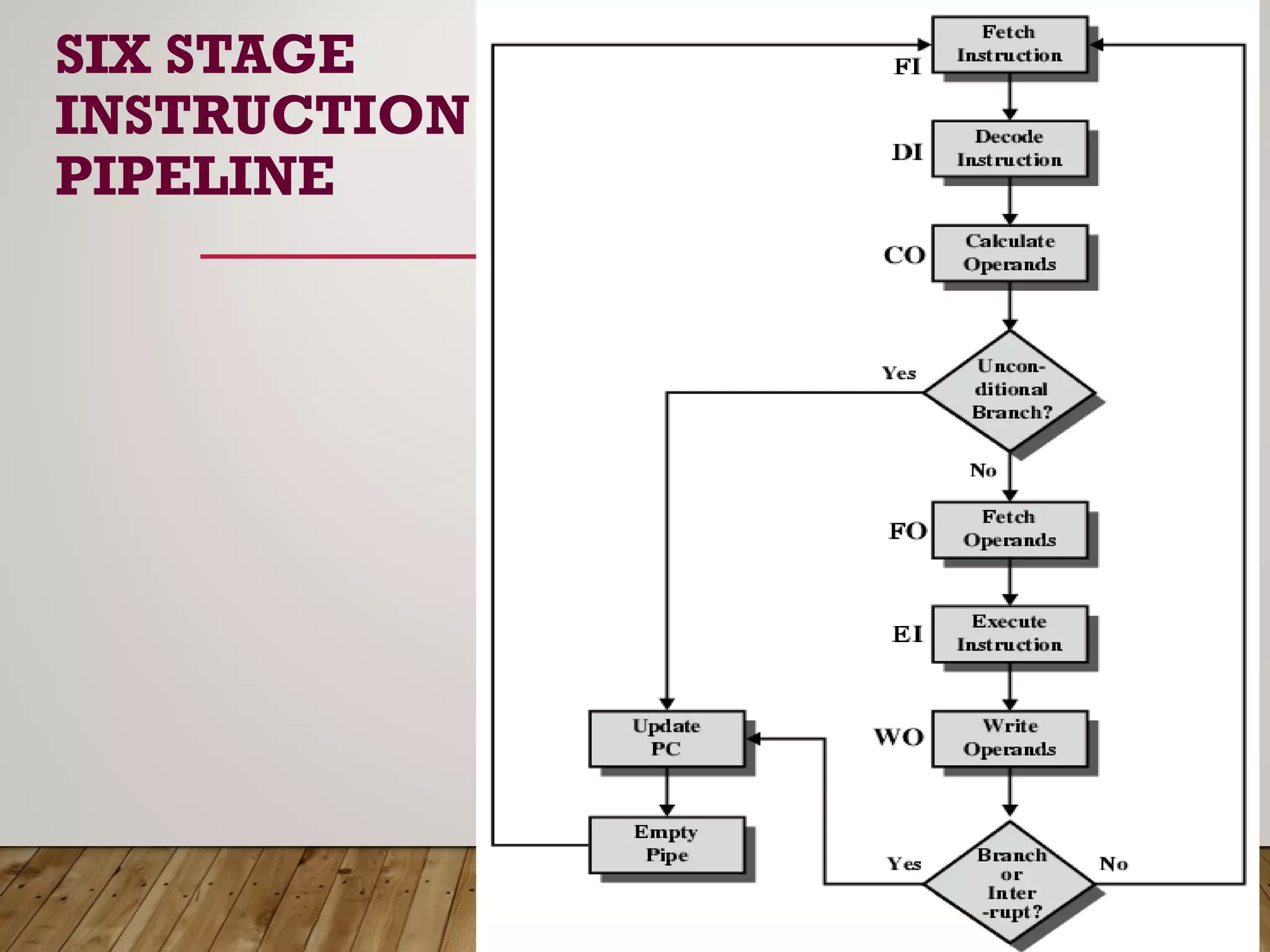

Pipelining is a technique where the instruction execution process is divided into multiple stages that can operate in parallel. This allows subsequent instructions to begin processing before previous ones have finished. For example, with laundry, pipelining allows washing, drying, and folding different loads simultaneously to complete all the laundry faster. In processors, pipelining overlaps the stages of instruction fetch, decode, execute, and writeback to improve throughput. While pipelining improves performance, it can introduce hazards like structural, data, and control hazards that must be addressed.