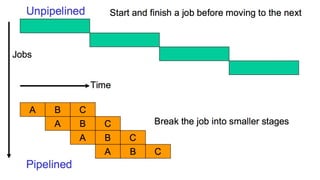

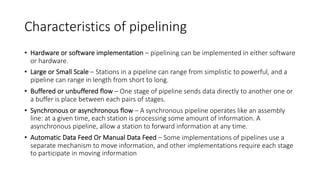

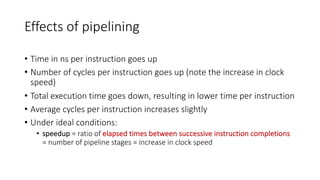

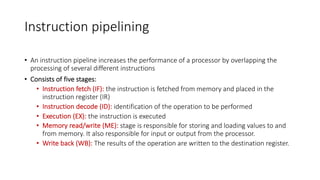

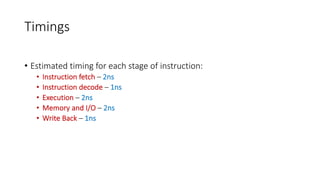

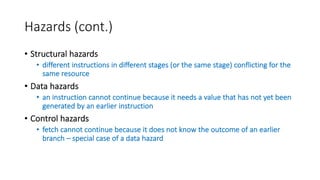

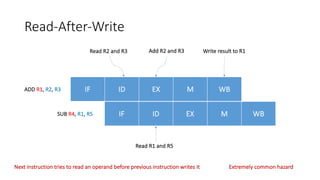

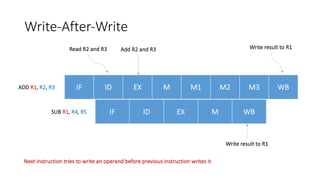

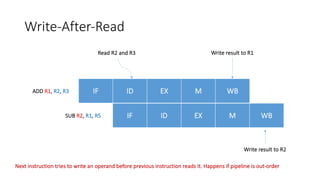

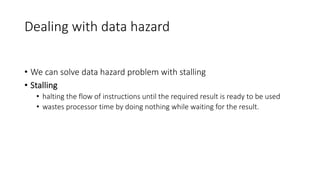

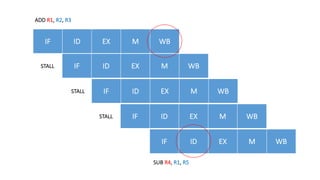

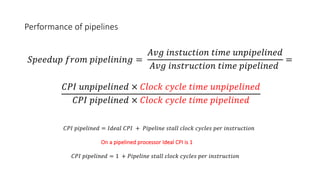

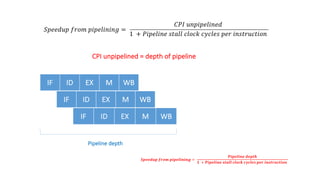

Pipelining is a microprocessor technique that allows simultaneous execution of multiple instructions by overlapping their execution stages, which can enhance performance. However, it faces challenges such as structural, data, and control hazards that can disrupt instruction flow and efficiency. While pipelining improves execution speed and resource management, it also requires additional hardware and may not always run at peak efficiency due to these hazards.