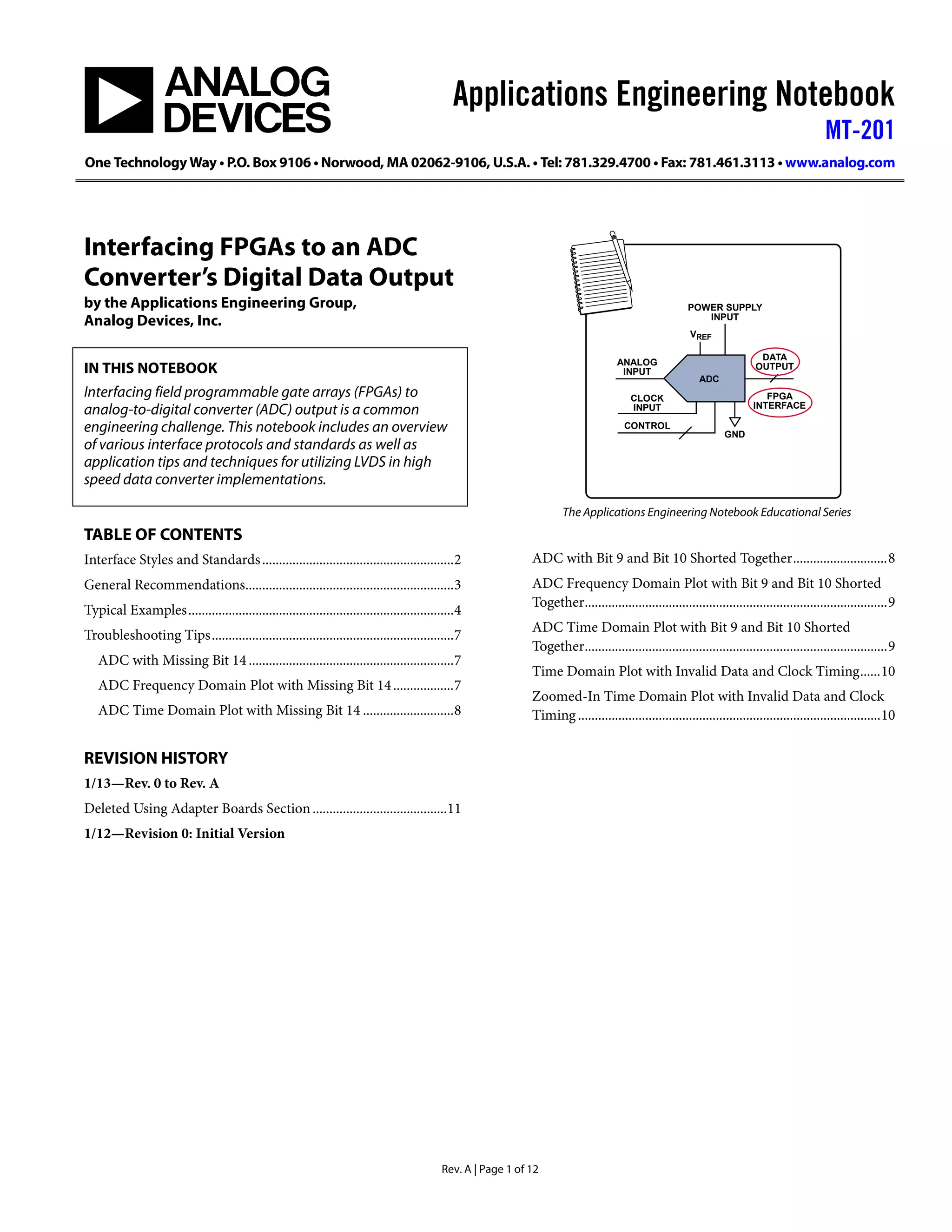

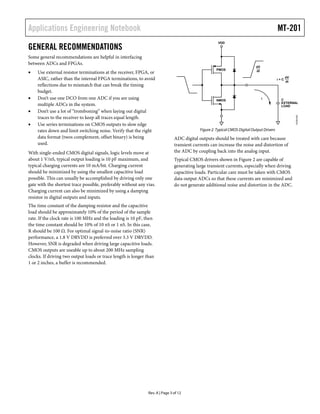

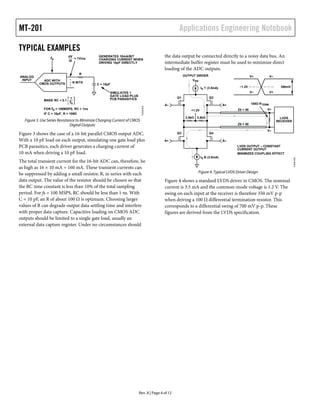

This document provides an overview of interfacing field programmable gate arrays (FPGAs) to analog-to-digital converter (ADC) outputs. It discusses various digital interface protocols and standards used by ADCs, including single data rate CMOS, double data rate CMOS, parallel low voltage differential signaling, serial LVDS, I2C, and JESD204. The document provides recommendations for minimizing noise when interfacing with CMOS outputs and examples of using series termination resistors. It also compares the ANSI and IEEE LVDS standards and shows the effects of trace length on signal integrity. Finally, it includes troubleshooting tips and examples of issues detectable from digital plots.