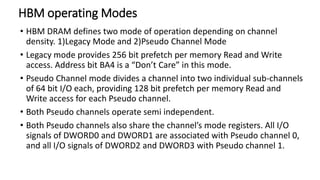

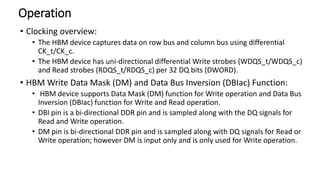

The document provides an in-depth overview of High Bandwidth Memory (HBM), including its features, operating modes, and standards such as HBM2 and HBM2E. HBM is utilized in various applications like GPUs, AI training, and high-performance computing, and it offers superior bandwidth and efficiency compared to traditional memory types. Key topics discussed include channel addressing, command operations, and the specifics of read and write procedures.

![• AUTO PRECHARGE:

• Auto Precharge is a feature which performs the same individual-bank precharge

function described as Precharge, but without requiring an explicit PRECHARGE

command.

• REFRESH Command (REF):

• The REFRESH command is used during normal operation of the HBM device. The

command is received on the row command inputs R[5:0] and requires a CNOP

command on the column command inputs C[7:0].

• Parity is evaluated with the REFRESH command when the parity calculation is

enabled in the Mode Register.

• SINGLE BANK REFRESH Command (REFSB):

• The SINGLE BANK REFRESH command provides an alternative solution for the

refresh of the HBM device. The command initiates a refresh cycle on a single

bank while accesses to other banks including writes and reads are not affected.](https://image.slidesharecdn.com/hbmhighbandwidthmemory-210328172842/85/High-Bandwidth-Memory-HBM-21-320.jpg)

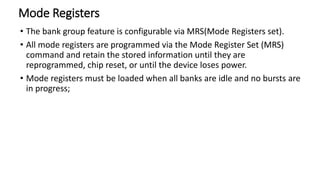

![• Mode Register Set (MRS):

• The MODE REGISTER SET (MRS) command is used to load the Mode Registers of

the HBM device. The command is received on the column command inputs C[7:0]

and requires a RNOP command on the row command inputs R[5:0].

• Power-Mode Commands:

• Power-Down is entered when CKE is registered LOW along with RNOP and CNOP

commands.

• CKE must not go LOW when read or write operations are in progress.

• CKE can go LOW while any other operations such as row activation, precharge,

auto precharge, or refresh are in progress, but the power-down specification will

not apply until such operations are complete.

• Self-Refresh (SRE, SRX):

• Self-refresh can be used to retain data in the HBM device, even if the rest of the

system is powered down. When in the self-refresh mode.](https://image.slidesharecdn.com/hbmhighbandwidthmemory-210328172842/85/High-Bandwidth-Memory-HBM-24-320.jpg)