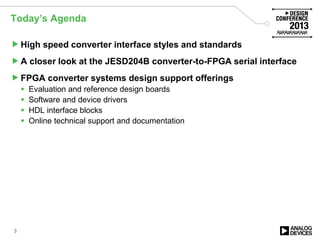

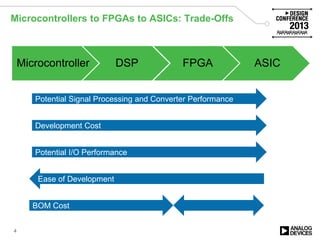

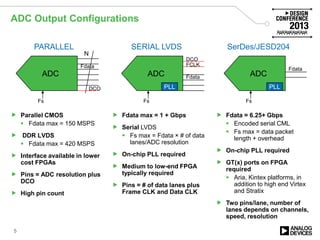

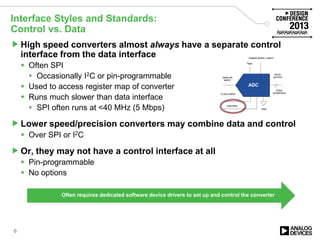

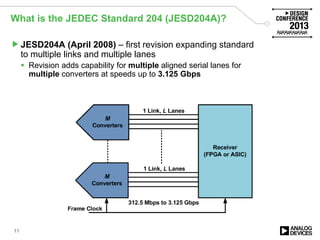

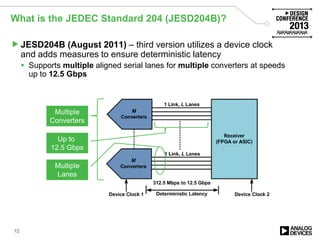

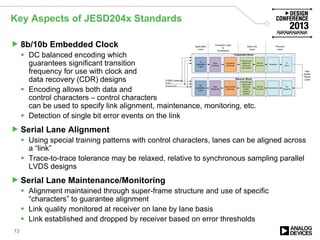

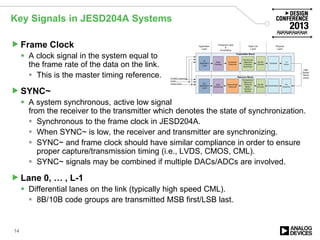

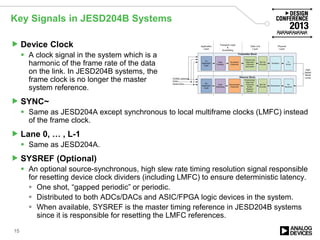

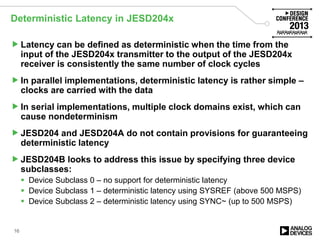

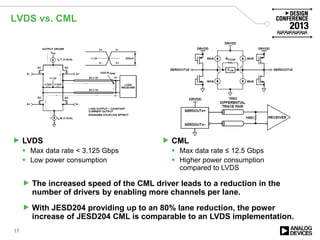

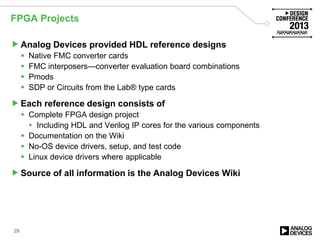

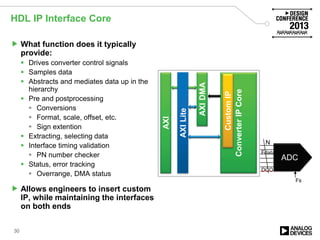

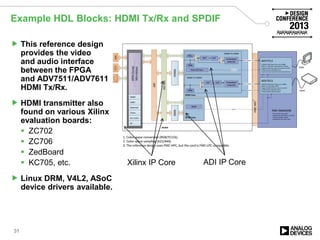

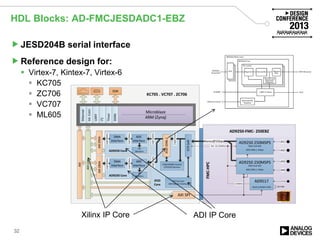

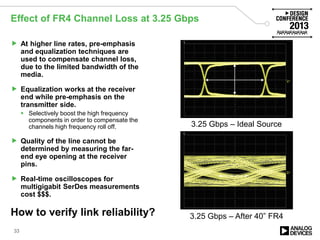

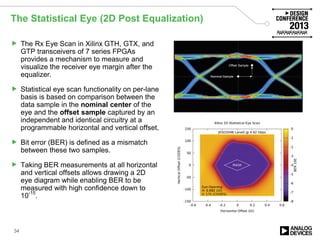

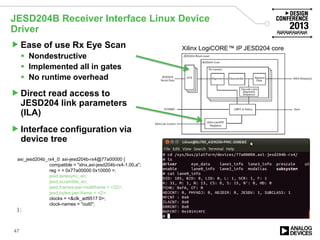

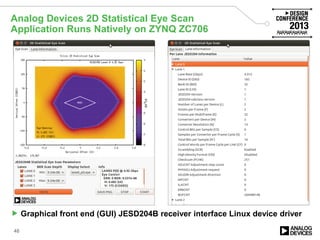

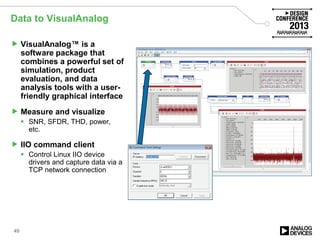

The document provides a comprehensive overview of high-speed data connectivity and the use of JESD204 standards for converter-to-FPGA serial interfaces. It addresses proprietary information, legal disclaimers, and offers insights into various interface styles, development costs, and ADC configurations. The content also details design support offerings, including evaluation boards, device drivers, and HDL interface blocks for effective system integration.

![Design Resources Covered in this Session

Design Tools and Resources:

Ask technical questions and exchange ideas online in our

EngineerZone™ Support Community

Choose a technology area from the homepage:

ez.analog.com

Access the Design Conference community here:

www.analog.com/DC13community

57

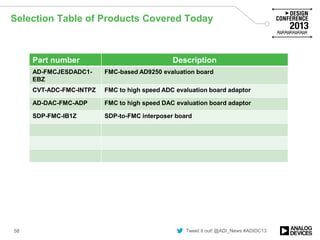

Name Description URL

VisualAnalog http://www.analog.co

m/visualanalog

Analog Devices

Wiki

Software and documentation

HDL interface code

Software device drivers

Reference project examples for FPGA connectivity

http://wiki.analog.com/

[other]](https://image.slidesharecdn.com/dc-13highspeeddataconnectivityfinal-130501142441-phpapp02/85/High-Speed-Data-Connectivity-More-Than-Hardware-Design-Conference-2013-54-320.jpg)