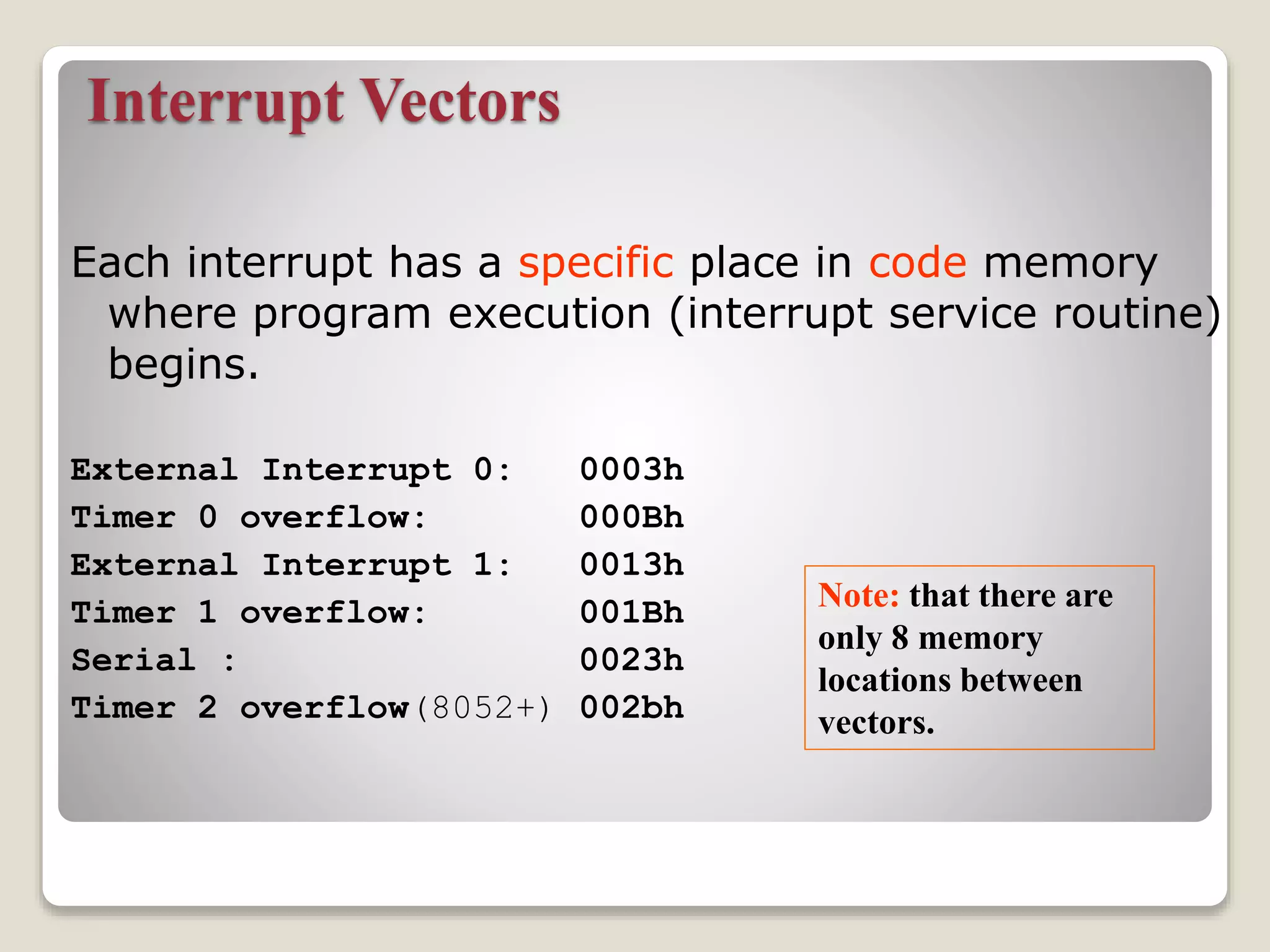

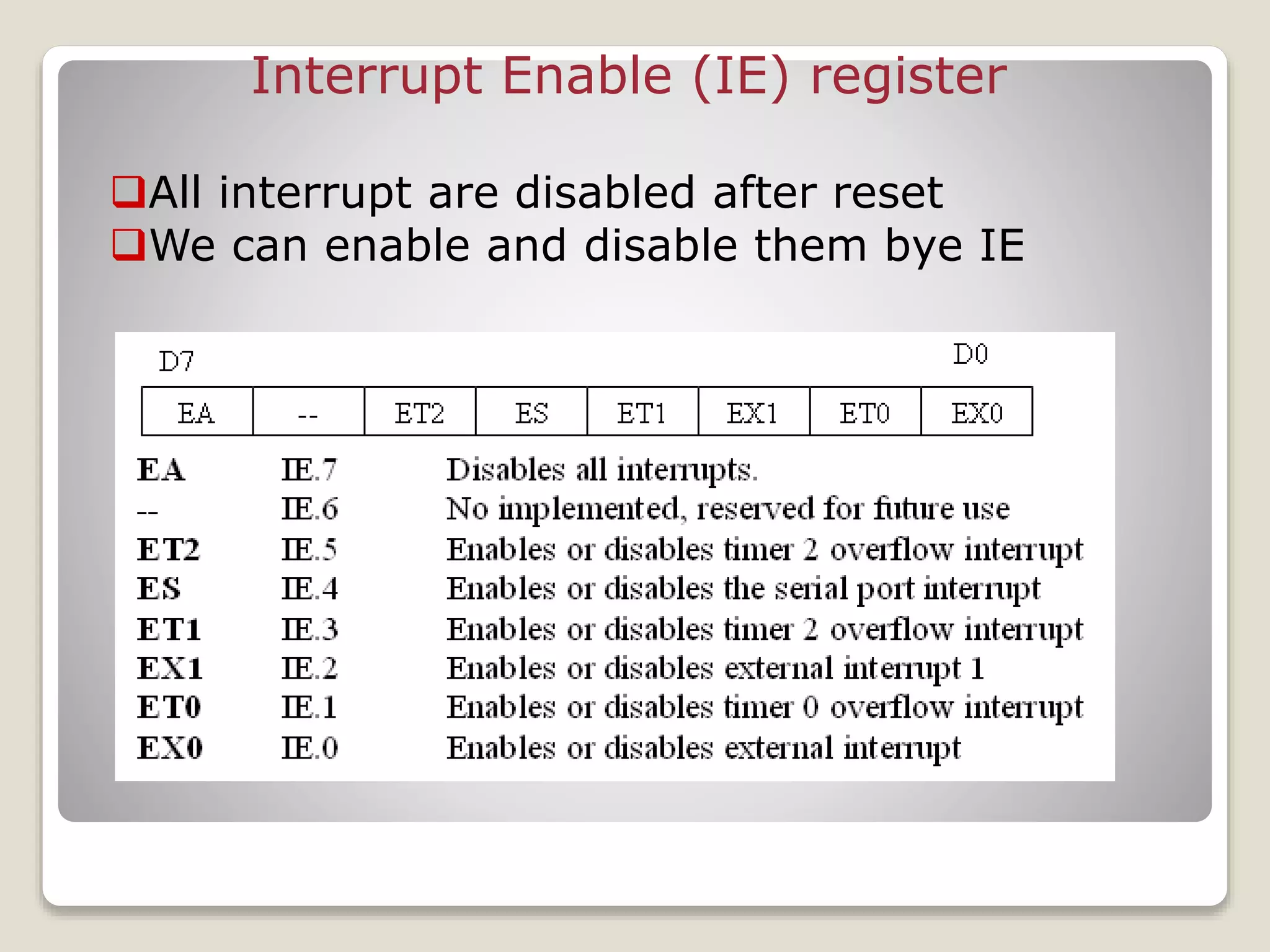

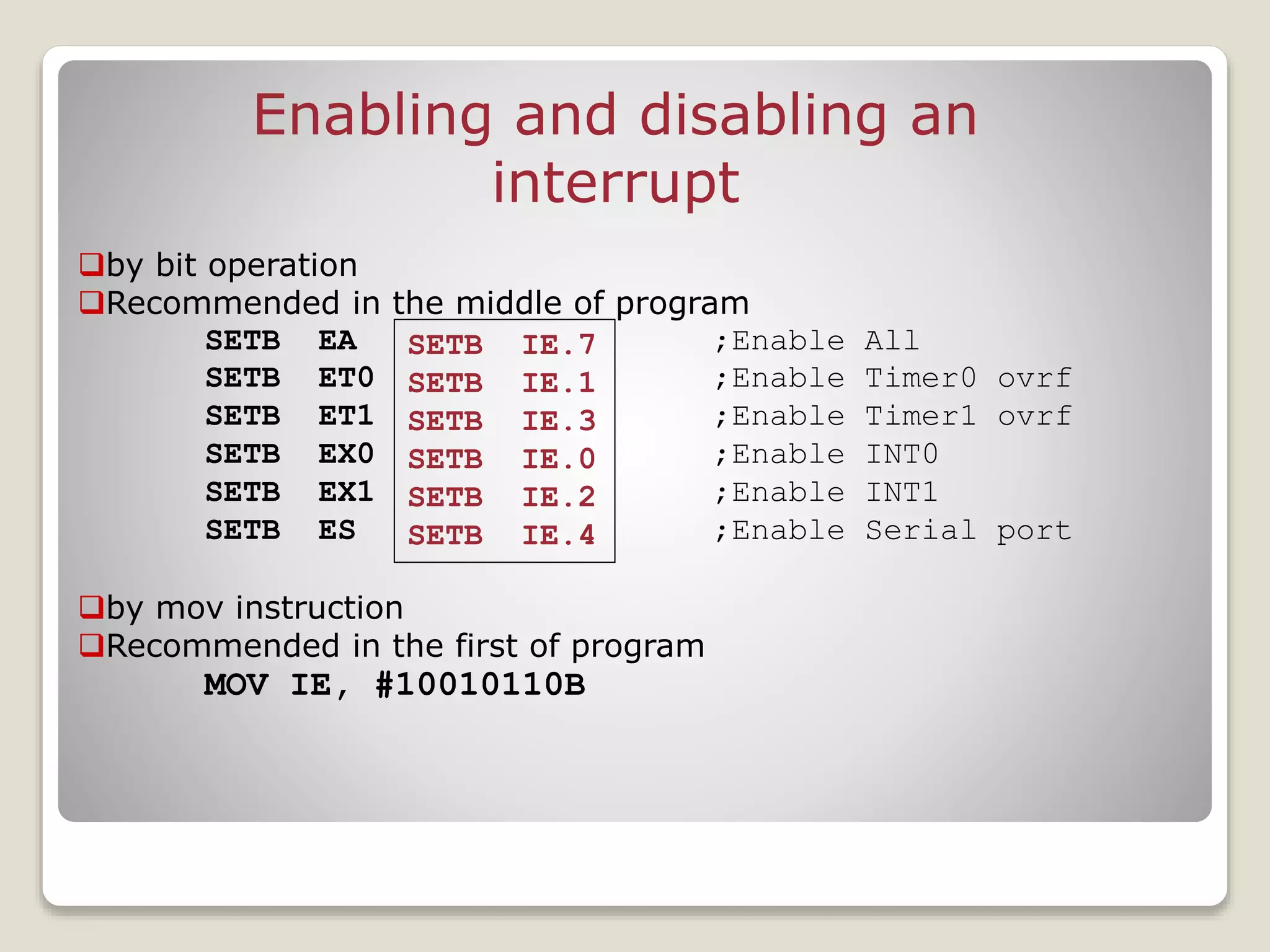

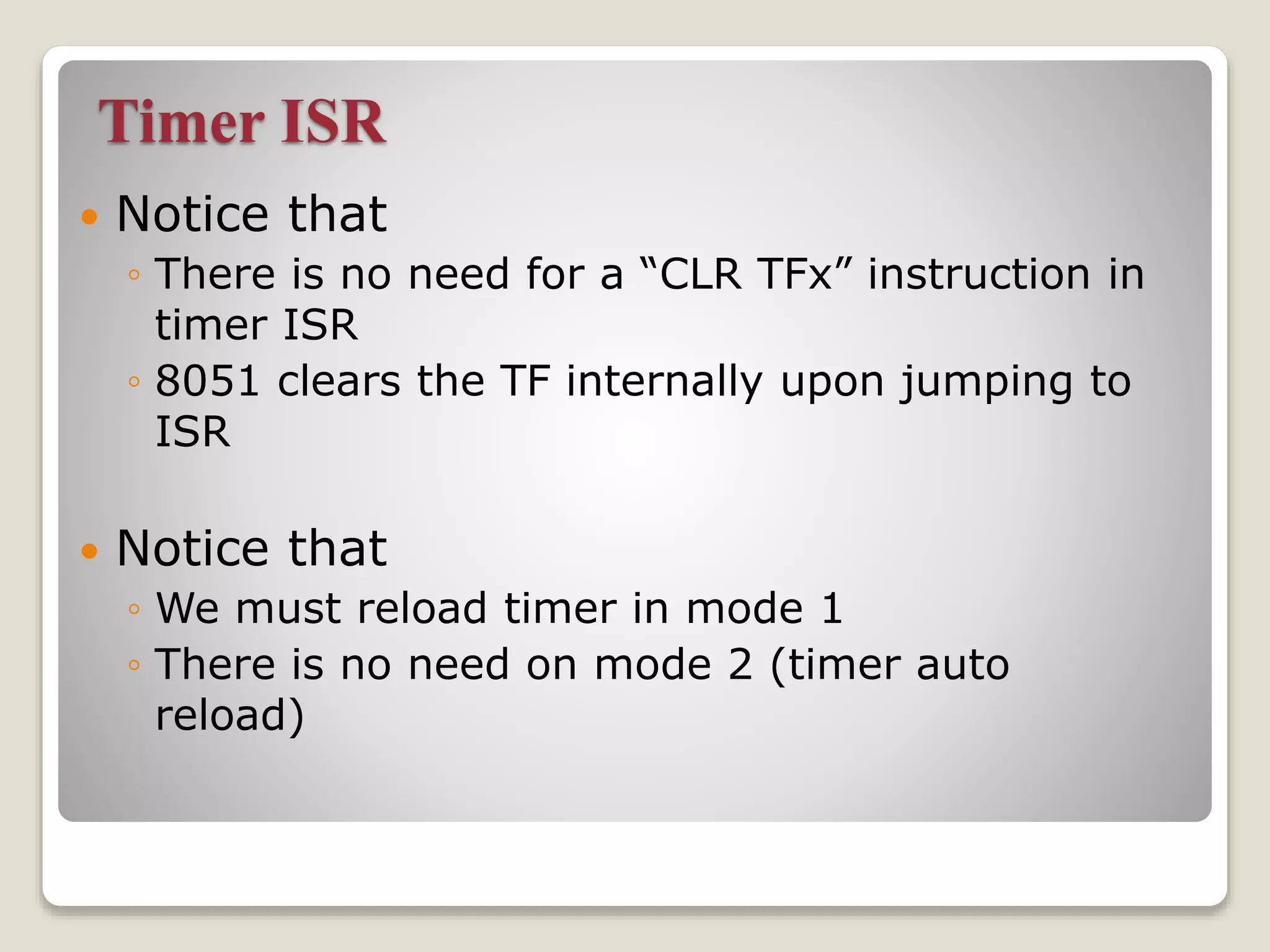

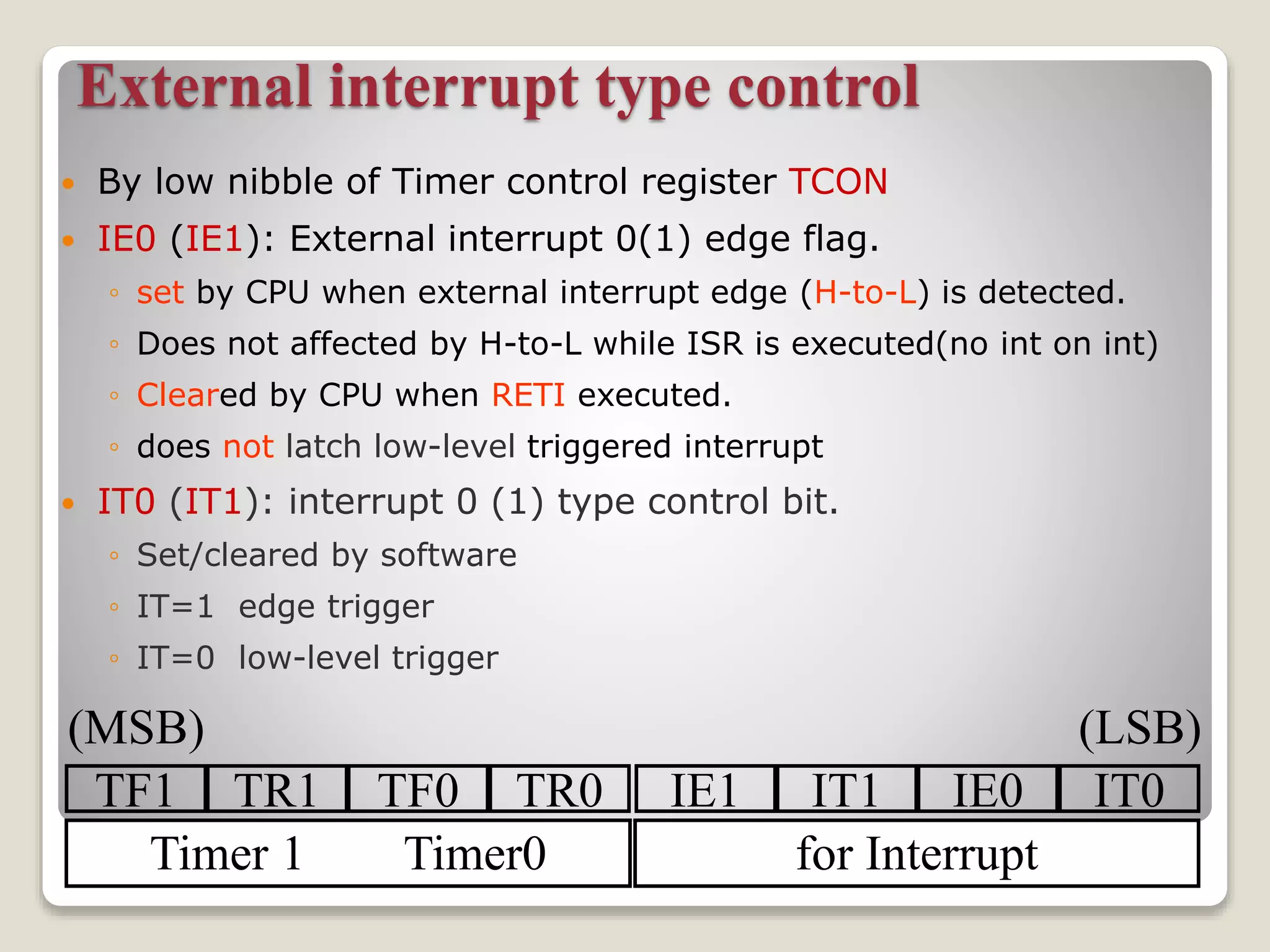

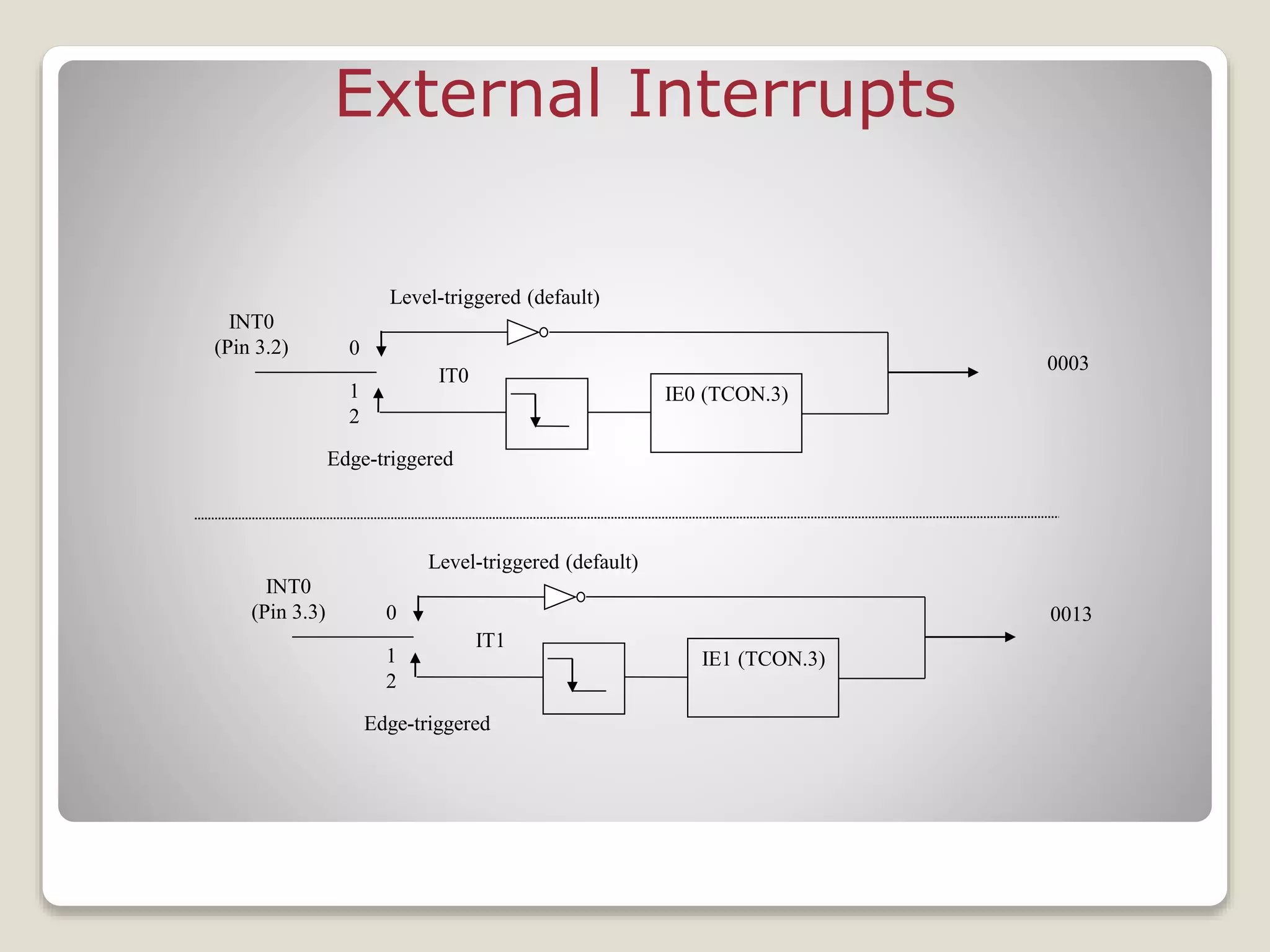

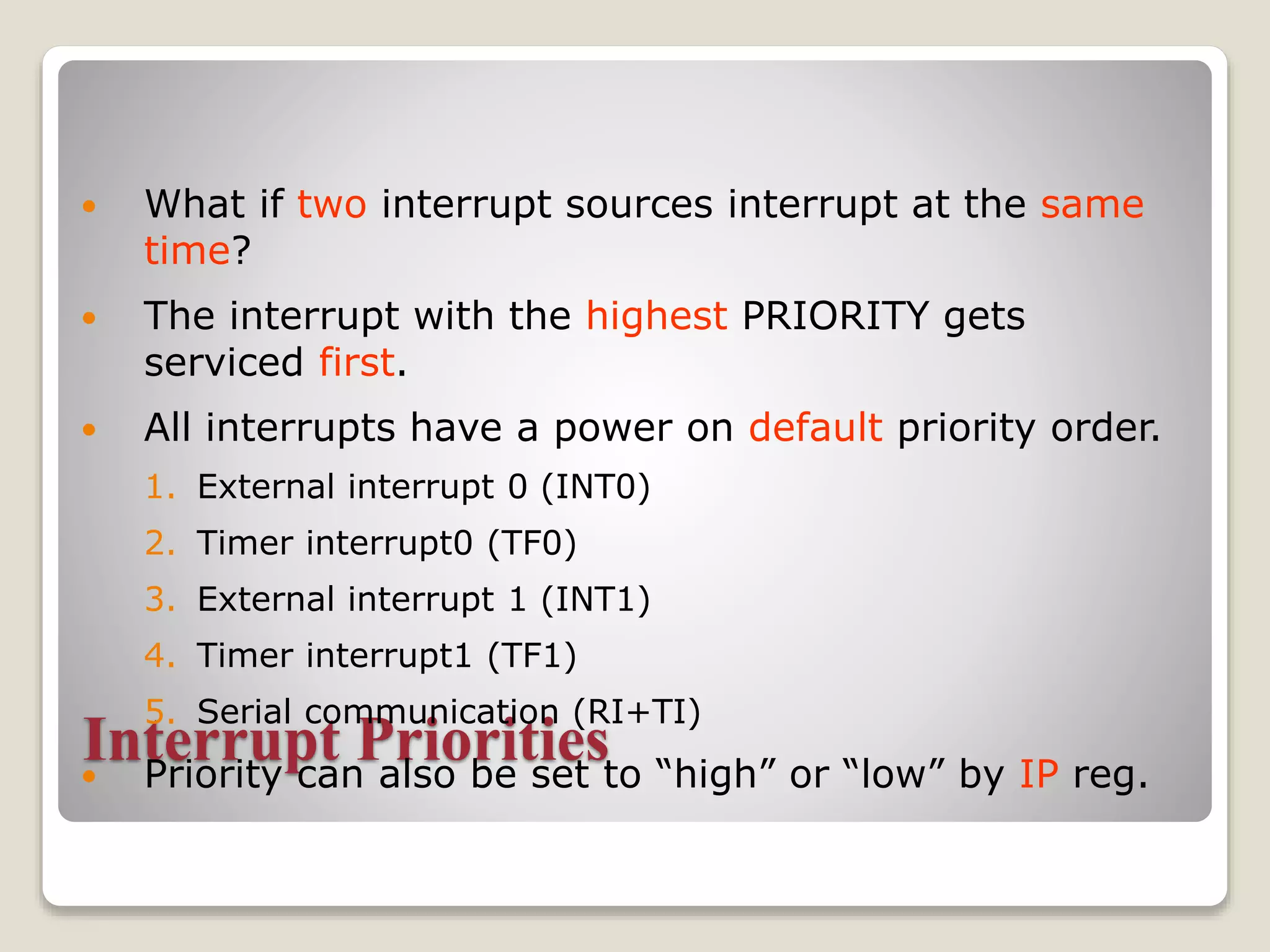

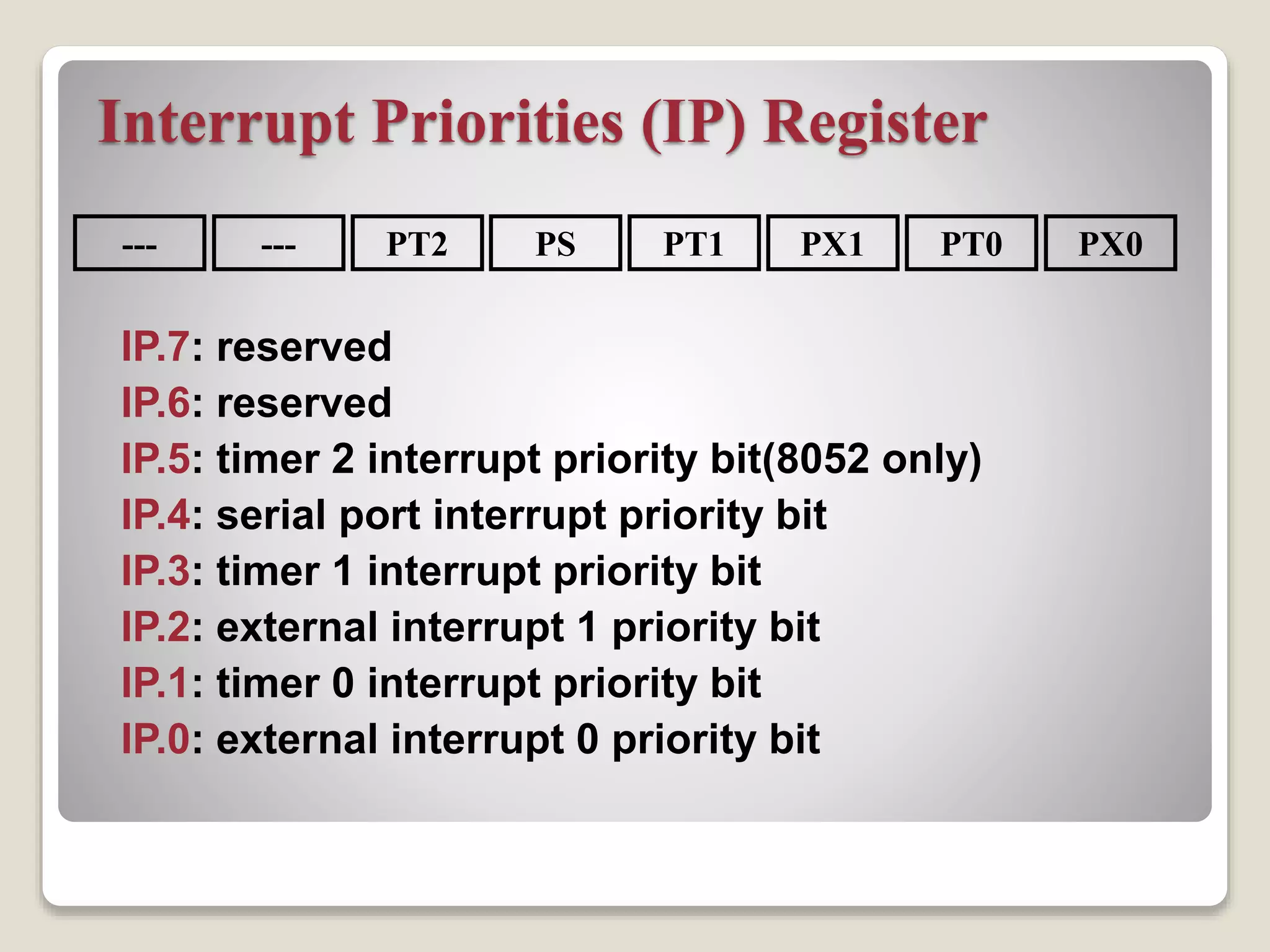

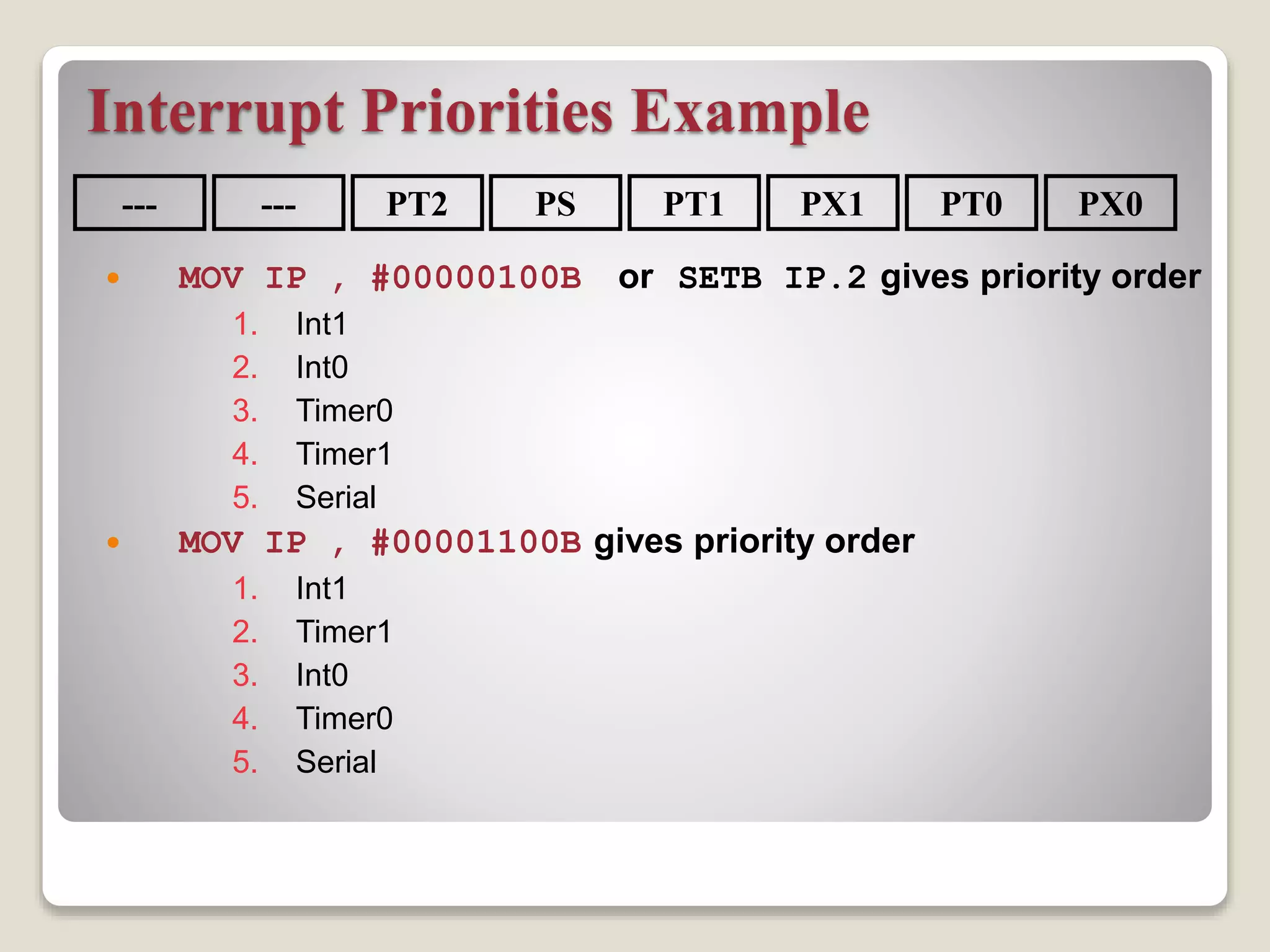

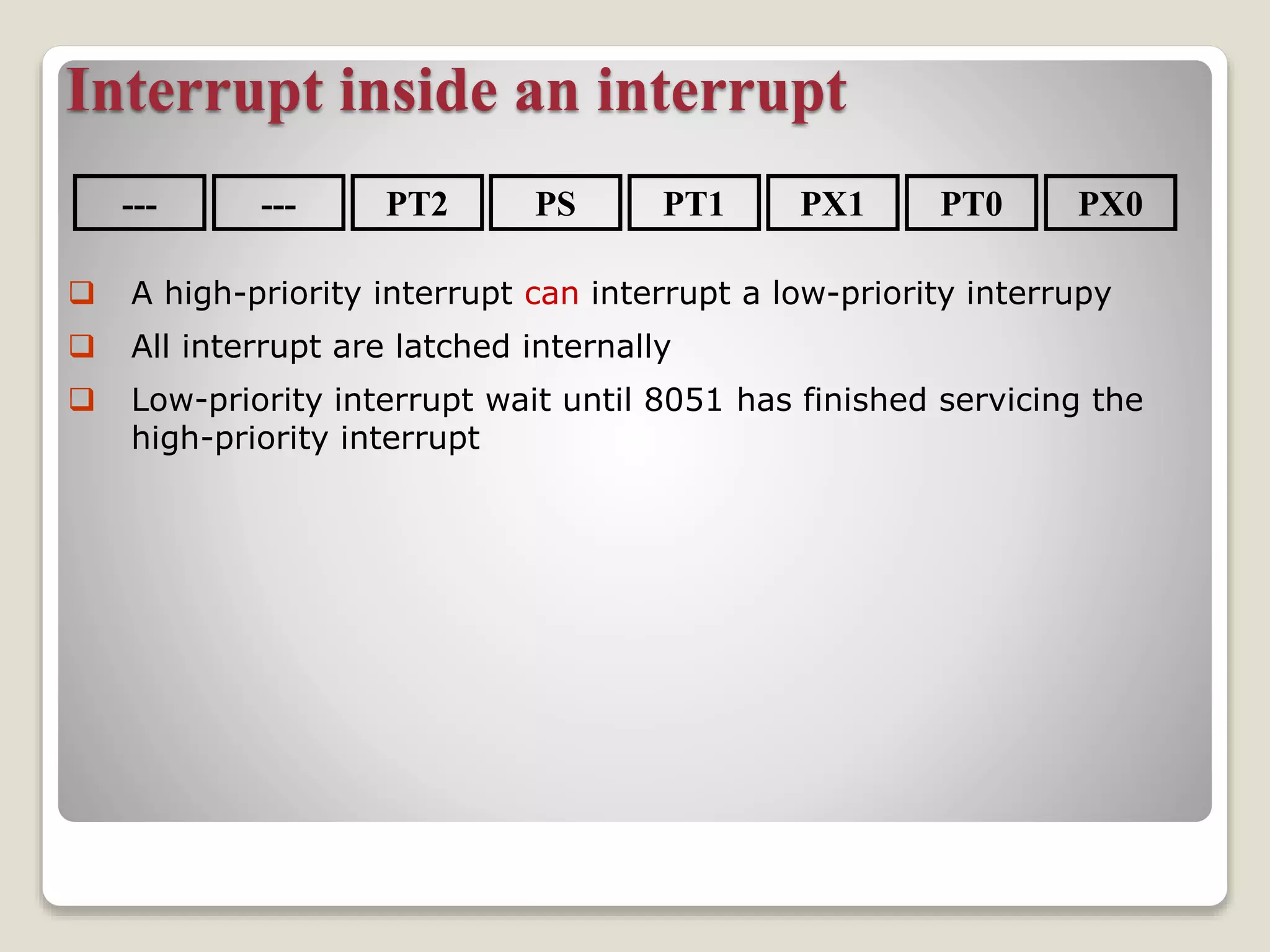

The document discusses the concept of interrupts in the 8051 microcontroller, explaining how they serve as signals from devices requiring service, in contrast to polling methods. It details the execution steps of interrupts, the types of interrupts available, and how to manage interrupt priorities, highlighting the advantages of using interrupts over polling. The document also outlines various interrupt sources and control mechanisms in the 8051 architecture.