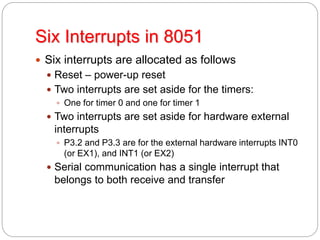

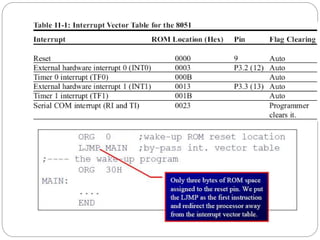

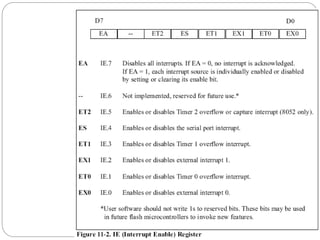

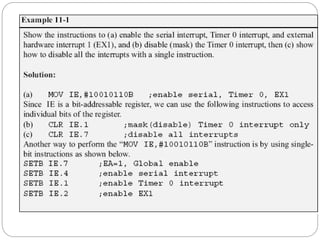

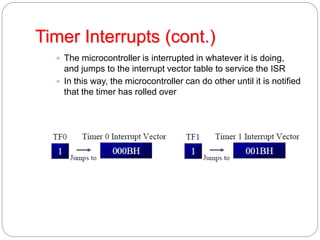

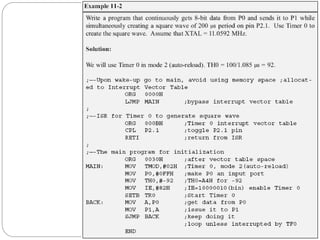

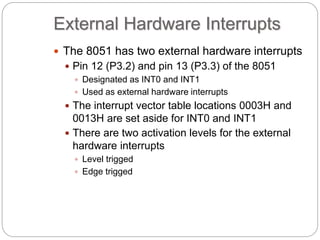

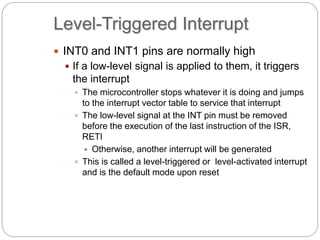

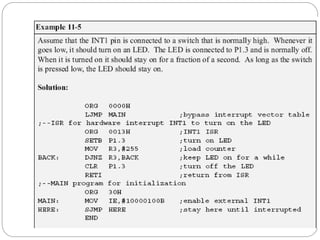

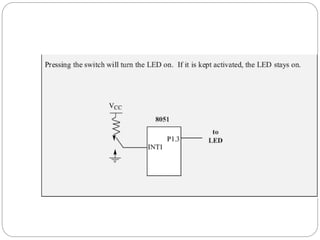

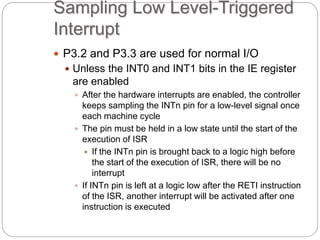

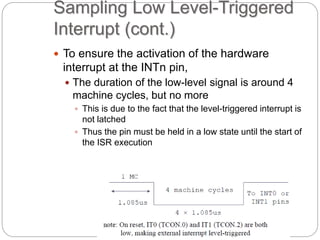

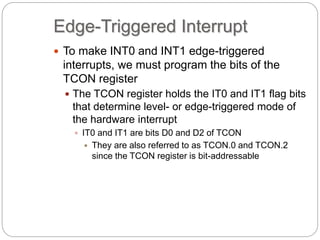

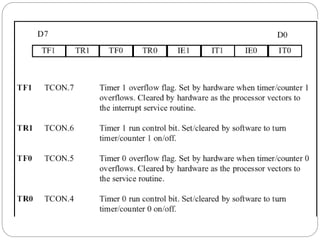

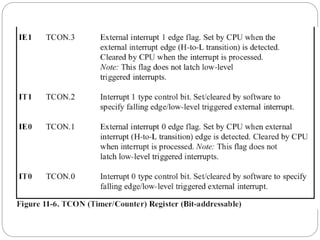

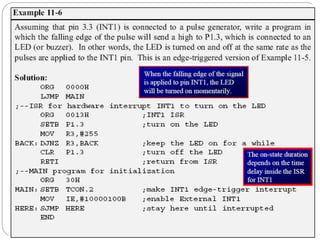

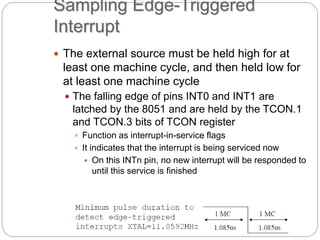

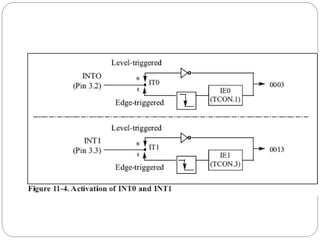

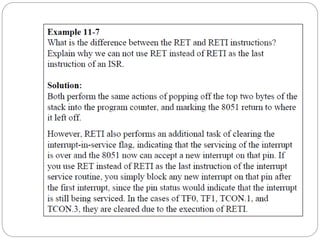

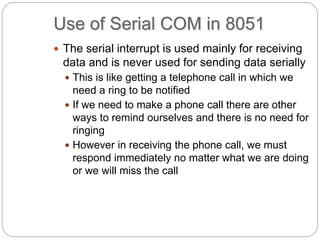

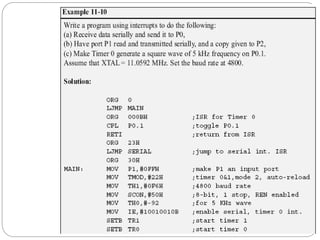

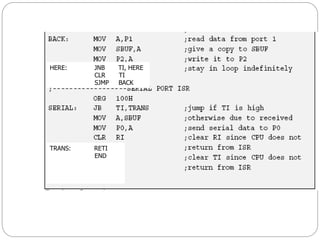

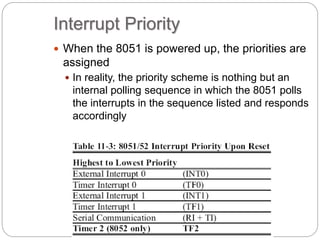

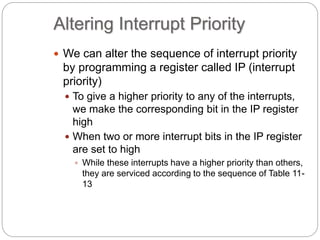

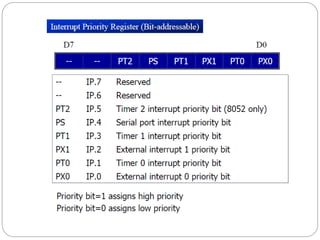

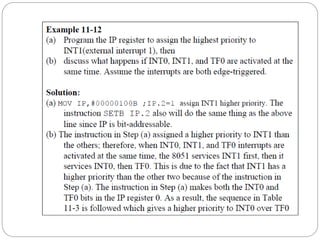

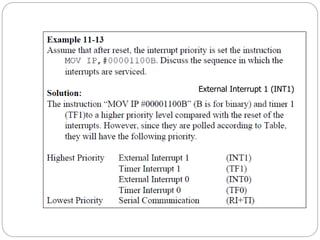

The document discusses interrupts in microcontrollers and compares interrupts to polling. It describes how interrupts allow a microcontroller to serve multiple devices simultaneously. When an interrupt occurs, the microcontroller saves its state and jumps to an interrupt service routine (ISR) to handle the interrupt. The document outlines the six interrupts in the 8051 microcontroller and how to enable, disable, and set the priority of interrupts. It also discusses timer, external hardware, and serial communication interrupts in detail.