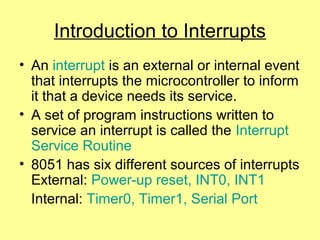

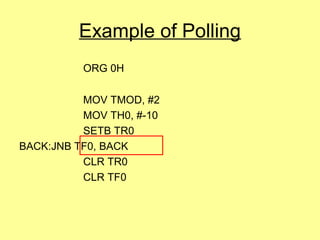

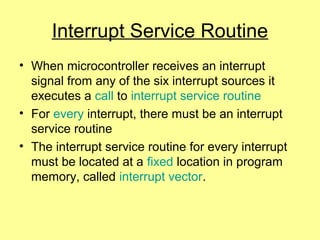

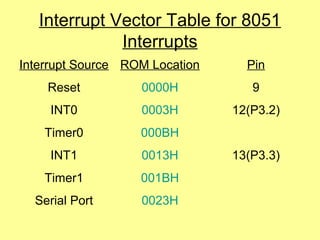

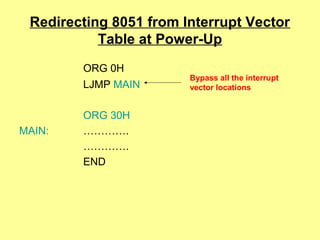

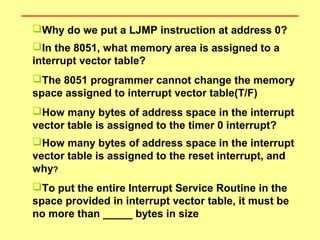

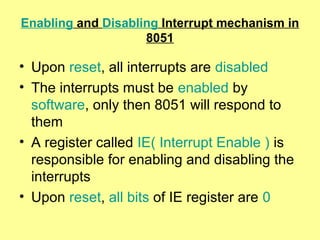

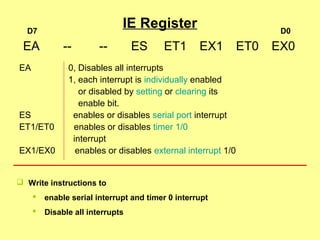

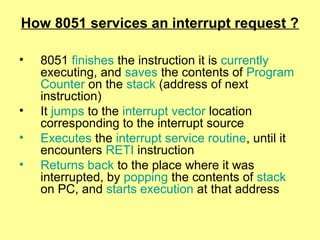

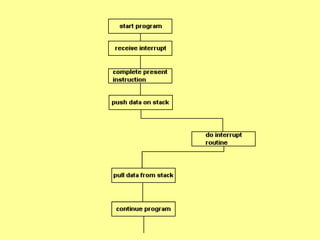

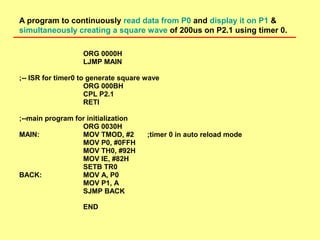

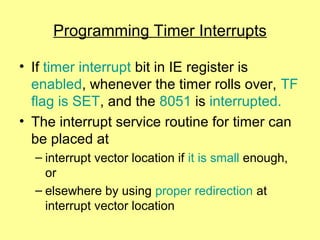

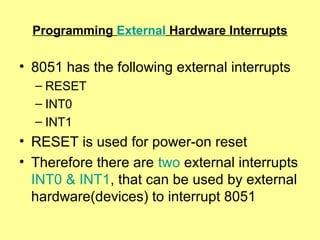

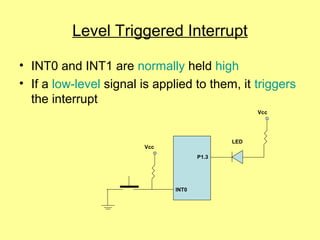

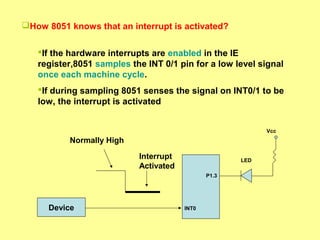

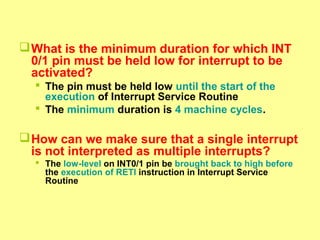

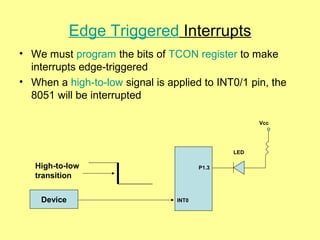

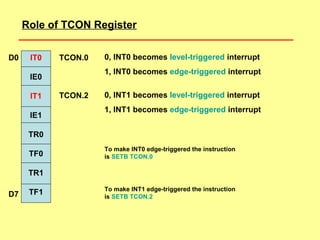

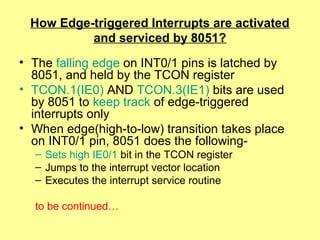

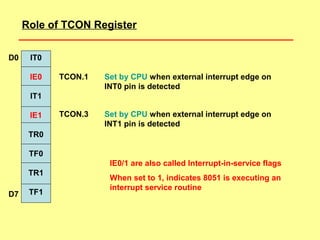

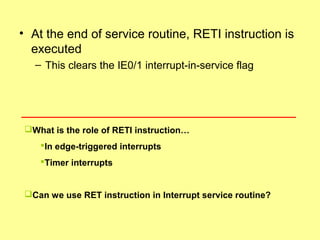

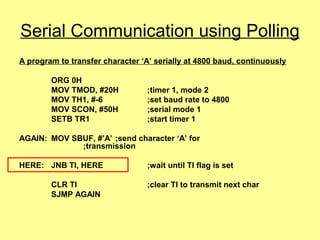

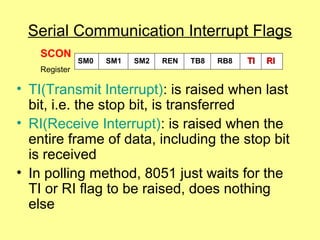

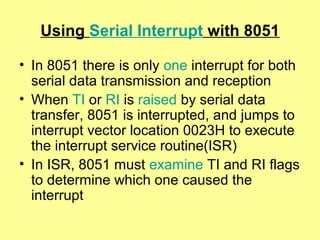

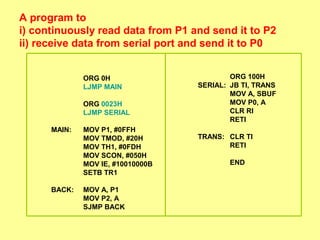

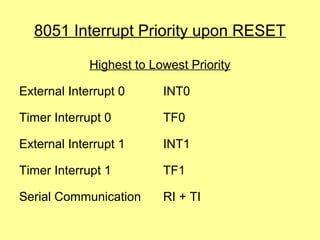

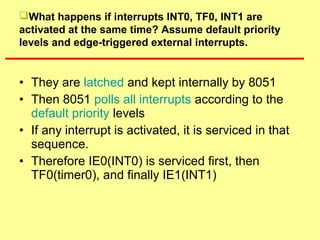

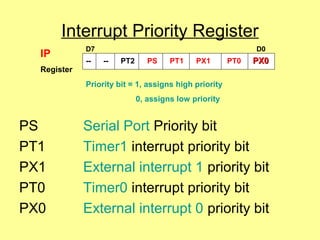

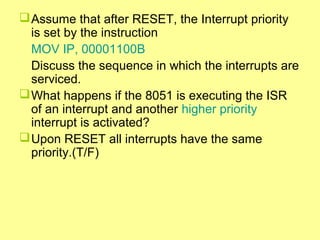

The document discusses the concept of interrupts in the 8051 microcontroller, detailing various sources of interrupts and the differences between interrupt handling and polling methods. It outlines how the microcontroller services interrupts through an interrupt service routine (ISR) linked to a fixed interrupt vector table and describes the mechanisms for enabling and handling interrupts for both internal and external sources. Additionally, it covers the role of registers such as the interrupt enable (IE) and tcon registers in managing and servicing interrupts, as well as programming examples related to both timer and serial communication interrupts.