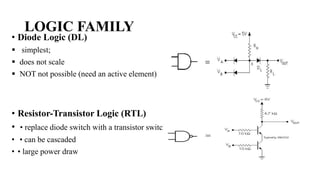

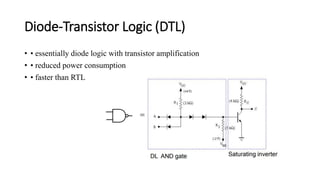

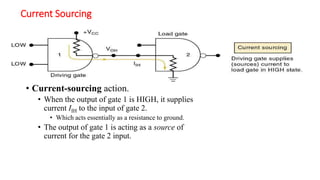

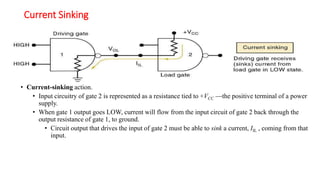

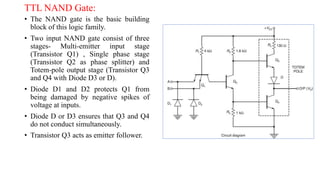

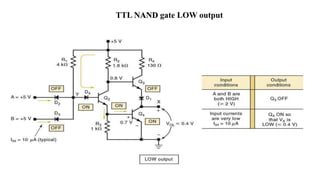

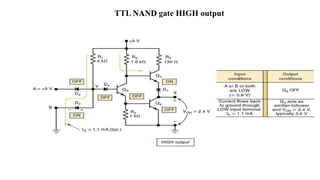

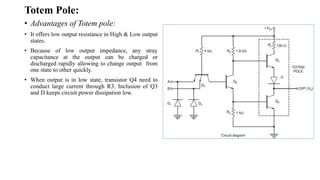

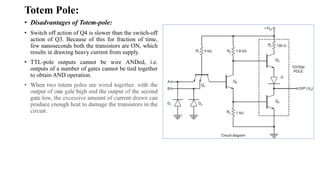

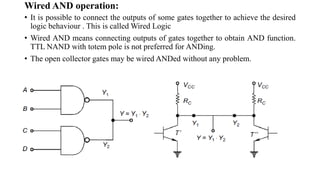

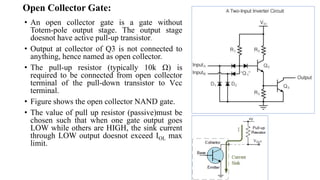

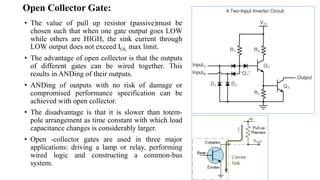

This document provides an introduction to different logic families including diode logic, resistor-transistor logic, diode-transistor logic, emitter-coupled logic, and transistor-transistor logic. It describes the characteristics and components of transistor-transistor logic gates including the TTL NAND gate structure with its input, phase splitter, and totem-pole output stages. It also discusses wired AND operation, open collector gates, and their advantages for interfacing logic families.