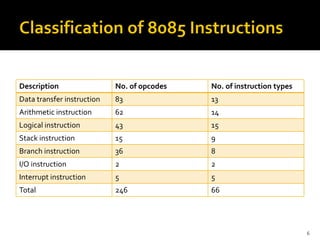

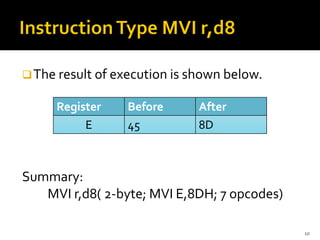

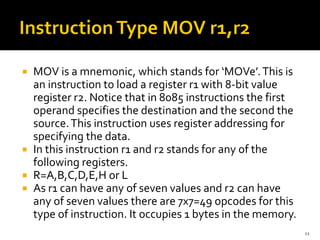

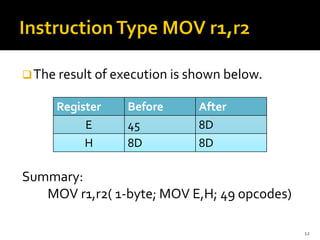

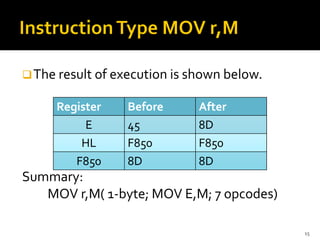

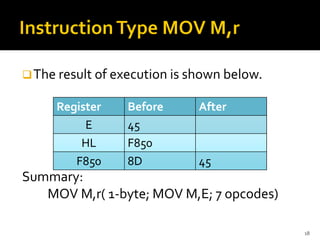

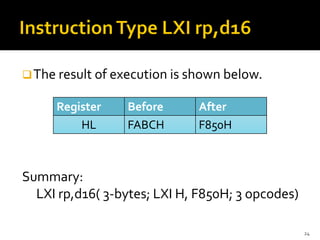

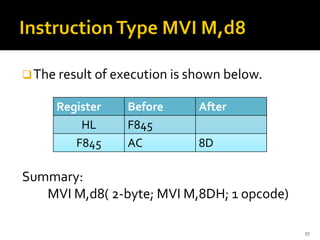

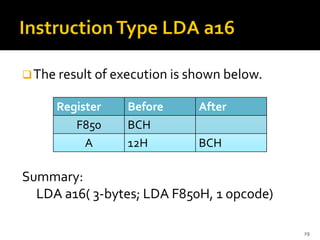

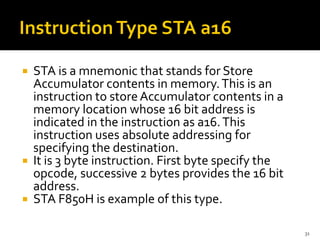

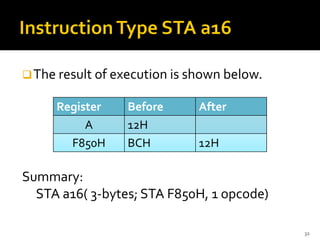

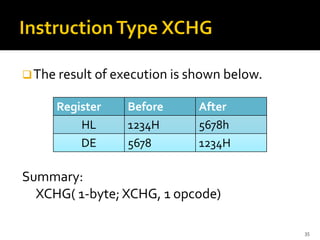

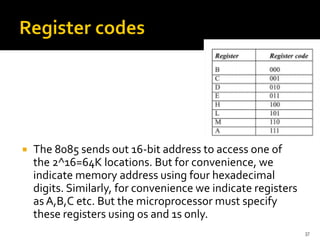

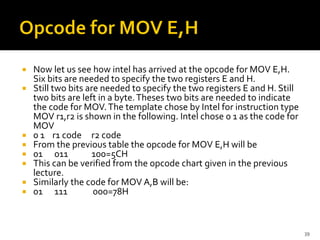

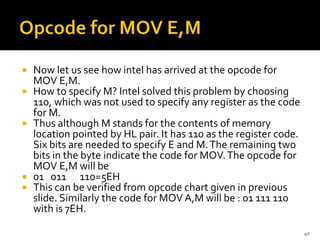

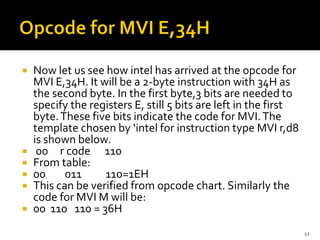

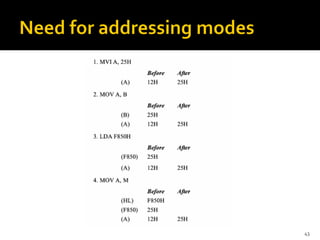

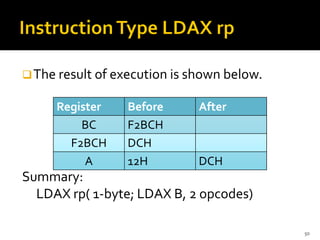

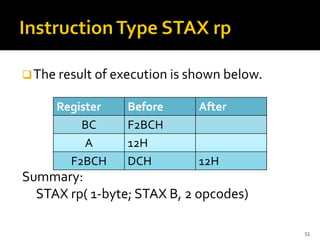

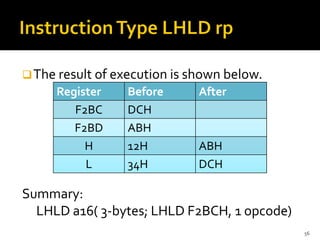

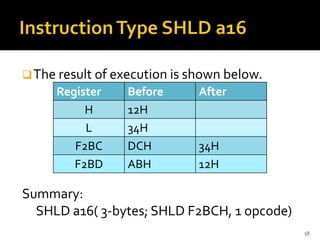

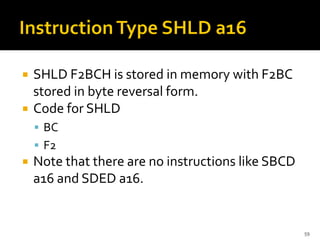

The document presents a detailed overview of the 8085 microprocessor instruction set, covering various instruction types and their related opcodes, including data transfer, arithmetic, logical, stack, branch, I/O, and interrupt instructions. It explains the addressing modes, such as immediate, register, absolute, register indirect, and implied addressing, as well as providing examples and execution results for specific mnemonics like MVI, MOV, LDA, and STA. Additionally, it discusses how opcodes are constructed and emphasizes that although 256 distinct opcodes are theoretically possible, only 246 are implemented in the 8085 architecture.